|

STELLA通信は㈱ステラ・コーポレーションが運営しています。 |

IDW'11~酸化物TFT編 |

||||||||||||||||||||||||||||||||||||||||||||

プロセスを若干工夫するだけでIGZO-TFTの特性を改善

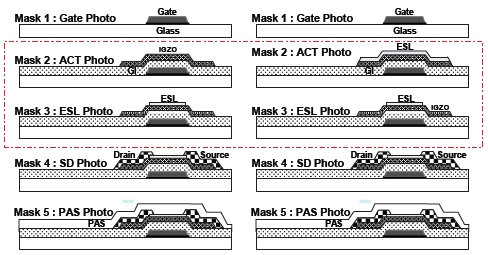

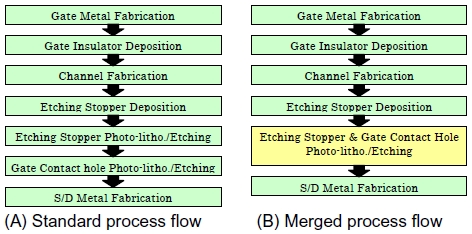

まず、酸化物TFTの王者としての地位を確立したa-IGZO(In-Ga-Zn-O)では量産が目前に迫っていることもあってか、デバイス信頼性に関する発表が目についた。そうしたなか、LG Displayはフォトリソ回数を増やさずにプロセスフローを工夫することによって初期特性&信頼性を高めることに成功した。 周知のように、コンベンショナルなボトムゲート型a-IGZO-TFTではソース/ドレイン形成時のフォトリソ工程やフォトレジスト剥離工程でチャネルがダメージを受けるのを防ぐため、チャネルの上部にエッチングストッパーを設けるエッチングストッパータイプが主流となっている。しかし、この構造でもチャネルに吸着する有機成分によるコンタミネーションがまったくないとは言い切れない。そこで、a-IGZO膜とエッチングストッパーを連続成膜し一括パターニングするプロセスを考案した。 今回の研究では2200×2500㎜の第8世代マザーガラス上にa-IGZO-TFTを作製した。ゲートメタルはCu膜をスパッタリング成膜、ゲート絶縁膜はSiO2膜をプラズマCVD成膜。a-IGZO膜は膜厚60nmで室温スパッタリング成膜した。続いて、SiO2エッチングストッパーをプラズマCVD成膜した後、Cu膜をスパッタリング成膜してソース/ドレインを形成。最後に、SiO2パッシベーションを膜厚300nmでプラズマCVD成膜した。チャネル長は11.4μm、チャネル幅は100μmである。 図1のように、スタンダードプロセスはa-IGZO膜を成膜しフォトリソでパターニングした後、エッチングストッパーを成膜しフォトリソでパターニングする。一方、改良プロセスはa-IGZO膜とエッチストッパー膜を連続成膜しフォトリソで一括パターニングした後、ソース/ドレインとのコンタクト領域を確保するため、エッチングストッパー膜を再度フォトリソでパターニングしてチャネル上部だけに残す。

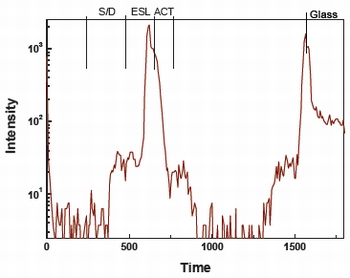

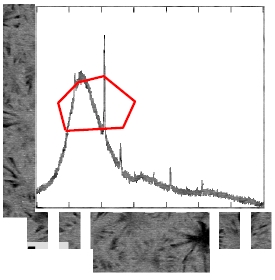

a-IGZO-TFT作製後、白色EL+COA(カラーフィルタ・オン・アレイ)方式のボトムエミッション型有機ELを形成した。具体的には、TFT上にRGBのCOAを形成した後、ITO画素電極を形成。その後、ホール輸送層、発光層、電子輸送層、カソードを真空蒸着した。 表1はスタンダードプロセスデバイスと改良プロセスデバイスの特性を比較したもので、ドレイン電圧を10Vに固定した場合、改良プロセスデバイスはモビリティが11.44cm2/V・s、Vthが1.24V、ON電流が111.24μA、Sファクターが0.17V/decとスタンダードプロセスデバイスに比べ良好な値が得られた。これは、上記のプロセスフローから一括パターニング時にエッチングストッパーがチャネルをプロテクトすることから、a-IGZO表面に有機コンタミネーションが発生しないためである。図2はスタンダードプロセスデバイスのSIMS深さプロファイル分析結果で、a-IGZO表面近傍にカーボン由来のピークが見える。つまり、a-IGZO膜のパターニング時におけるフォトリソ工程やレジスト剥離工程によってカーボンが拡散し表面を汚染する。

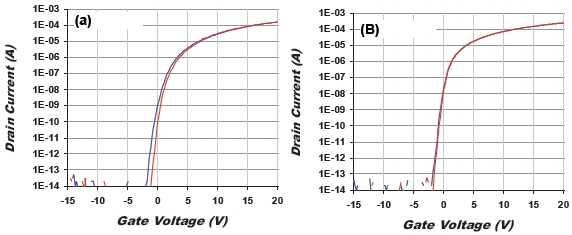

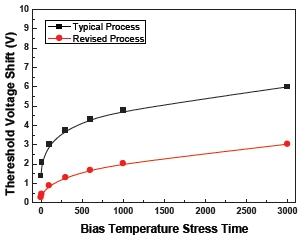

図3はソース/ドレイン電圧を10V、ゲート-ソース電圧を-15~+20Vにした際のトランスファー特性で、改良プロセスデバイスの電圧はドレイン電流1nAで0.05Vだった。これは、0.36Vだったスタンダードプロセスデバイスに比べ十分小さく、ヒステリシスも小さいことがわかる。つまり、a-IGZO-TFTの電気特性は活性層とエッチストッパー界面の状態に強く依存するわけである。 その出力特性も測定したところ、改良プロセスデバイスのソース/ドレイン電流はスタンダードプロセスデバイスよりも高かった。図4に60℃で30Vのポジティブバイアスを3000秒印加した際のVth変動を示す。Vthシフトは改良プロセスデバイスが2.76Vだったのに対し、スタンダードプロセスデバイスはその2倍程度だった。 参考として、写真1に上記の改良プロセスで作製したa-IGZO-TFT駆動の31型有機ELDを示す。なお、サブピクセル回路は数個のTFTと2キャパシタで構成した。 IGZO膜をスタックして光照射時のVthシフトを抑制 一方、富士フイルムは世界最高クラスのハイモビリティを備え、かつa-IGZO-TFTにとって唯一の弱点とされる光照射時における特性変動を解消したデバイスを報告した。周知のように、光照射環境下ではa-Si TFTほどではないものの、a-IGZO-TFTも比較的大きなVthシフトが観測される。このおもな原因としては、チャネル~ゲート絶縁膜界面に酸素欠損が発生するためといわれる。そこで、デバイス構造を工夫することでこの問題を解消することにした。 まず、In:Ga:Zn=1:1:1組成のa-IGZO膜を成膜しアニールした後、酸素拡散深さを調べた。SIMS分析の結果、アニール温度が350℃以上になると膜から酸素拡散が起こり、450℃では酸素拡散深さが15nmに達することがわかった。そこで、この酸素拡散を敢えて積極的に利用するデバイス構造を考案した。 試作デバイスは、まず熱酸化SiO2膜(膜厚100nm)付きシリコンウェハー上にIn1.85Ga0.15ZnO4膜を膜厚5nm、続いて第1耐熱レイヤーとしてIn0.5Ga0.15ZnO4膜を膜厚Xnmでマグネトロンスパッタリング成膜した。X膜厚は8nm(TFT-A)と50nm(TFT-B)にした。この後、O2雰囲気において450℃でアニール。さらに、TFT-Aは第2耐熱レイヤーとしてIn0.5Ga0.15ZnO4膜を膜厚50-Xnmで成膜した。続いて、Ti/Au(10nm/40nm)膜をメタルマスク越しにスパッタリング成膜してソース/ドレインをダイレクト形成。最後に、オーミックコンタクト性を確保するため、O2雰囲気において450℃でアニールした。

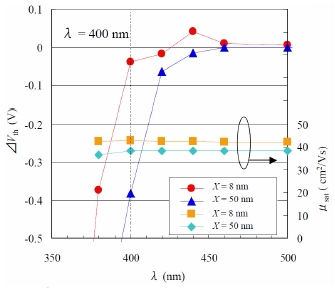

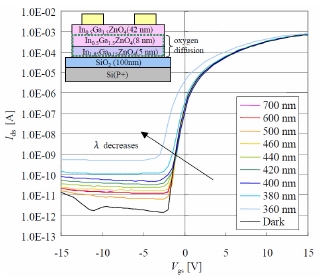

光照射下における応答性を評価するため、Xeランプから360~700nmの光を照度100μW/cm2で照射。この際、トランスファー特性はダーク状態と照射後の値を測定した。 図5にTFT-AのVgs-Ids特性を示す。ダーク状態ではTFT-Aが41.8cm2/V・s、TFT-Bが38.4cm2/V・sとともに最大のモビリティを示した。また、図6-右軸のようにどちらも可視光を照射してもモビリティはほとんど変化しなかった。 一方、Vthは光照射によって図6-左軸のように大きく変化した。具体的には、どちらのデバイスとも照射波長が440nm以上ではほとんど変化しなかったが、400nm以下になると大きな違いがみられ、400nmではTFT-Aはわずか0.04Vしかシフトしなかったのに対し、TFT-Bは0.38Vもシフトした。 こうした違いは酸素拡散効果によると考えられる。つまり、X=8nmであるTFT-Aでは450℃でアニールすると酸素拡散が深さ15nmにまで達するため、In1.85Ga0.15ZnO4チャネルのバルク領域における欠陥がIn0.5Ga1.5ZnO4耐熱レイヤーとの界面で酸素原子によって相殺されるからである。この結果、TFT-Bに比べ欠陥密度が低くなる。したがって、Vthシフトが抑制されるわけである。つまり、このデバイス構造ならばハイモビリティを維持したまま、光照射環境でのVthシフトも抑制できる。 成膜時にNをパージしてa-IGZO:Hに

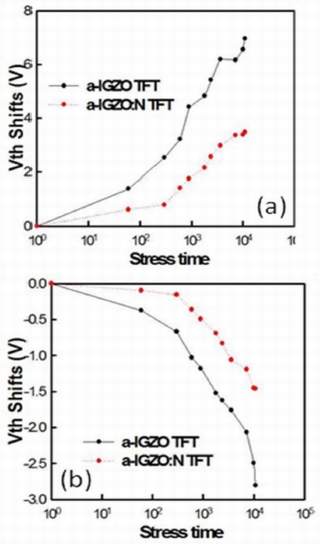

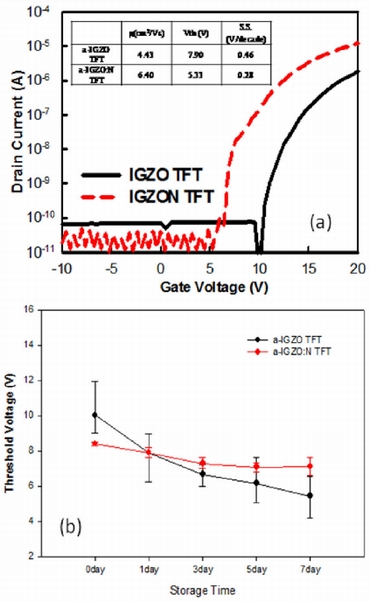

台湾のNational Chiao Tung Universityも、Vthシフト抑制という観点からa-IGZOにNをドープするというシンプルな方法を紹介した。結論から述べるとバイアスストレステストや光照射環境でVthシフトが抑制できただけでなく、モビリティをはじめとするイニシャル特性も向上するという。 実験では、シリコンウェハー基板上にボトムゲート型デバイスを作製した。まず、650℃でアニールして基板表面に熱酸化SiO2膜を形成しゲート機能を付与。続いて、In:Ga:Zn:O(1:1:1:4)ペレットを用いてa-IGZO膜を室温、パワー100W、圧力5×10-3torrでリアクティブスパッタリング成膜した。膜厚は50nmである。この際、Arガス(10sccm)に加え、Nガスを流量2sccmでパージした。この結果、活性層はa-IGZO:Nになる。なお、スパッタリング成膜はメタルマスクを介して行ったため、フォトリソによるパターニングは不要である。続いて、ITO膜を膜厚50nmでスパッタリング成膜し、ソース/ドレインとしてパターニング。最後に、350℃×1時間アニールした。 図7-(a)に試作デバイスのトランスファー特性を示す。モビリティはa-IGZO TFTが4.43cm2/V・s、a-IGZO:N TFTが6.4cm2/V・sで、Vth、Sファクターとも後者の方が低い値を示した。また、デバイスを大気中に放置して特性変動を評価したところ、図7-(b)のようにVthシフトはa-IGZO TFTが2.23V、a-IGZO:N TFTが1.28Vだった。さらに、a-IGZO:N TFTは時間の経過とともにVthシフト量が緩やかになった。 図8-(a)はポジティブバイアス、(b)はネガティブバイアスを104秒印加した際のVth特性で、a-IGZO TFTのVthシフトは前者で6.96V、後者で-2.8Vだった。これに対し、a-IGZO:N TFTのVthシフトは前者で2.97V、後者で-1.7Vだった。これは、外部環境に鈍感なNをパージすることによってa-IGZO膜中における酸素原子の吸収や脱離が抑制されるためと考えられる。つまり、a-IGZO:N TFTは信頼性の面でも優れているといえる。

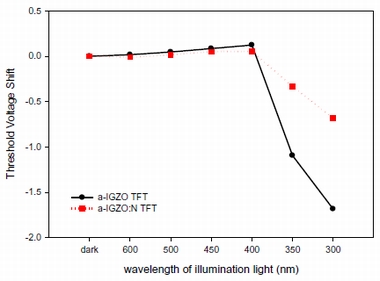

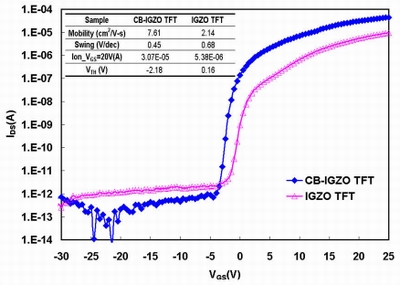

図9は波長300~600nmの光を照射した際のVthシフトで、両デバイスとも照射波長が400~600nmの場合、Vthはほとんど変動しなかったが、350nm以下のUV波長になるとVthシフトが大きくなった。しかし、この場合でもa-IGZO:N TFTのVthシフトはa-IGZO TFTより少なかった。 チャネルへのCu拡散を抑制してIGZO-TFTの安定性を改善 AU Optronicsは、a-IGZO TFTでソース・ドレインにCuを用いた際に問題となるチャネルへのCu拡散を抑制する方法を報告した。 試作デバイスは、①Cu膜を成膜しゲートを形成、②SiNx膜をプラズマCVD成膜しゲート絶縁膜を形成、③a-IGZO膜をDCスパッタリング成膜し酸化物半導体層を形成、④SiOx膜をプラズマCVD成膜しエッチングストッパーを形成、⑤Cu膜を成膜しソース/ドレインを形成、⑥Cuの拡散を抑制するCuブロック(CB)プロセスを追加、⑦SiOx膜を成膜しパッシベーションを形成、といったフローで作製。最後にN2雰囲気でアニール処理した。ここで⑥のCBプロセスを適用したデバイスをCB-IGZO TFT、CBプロセスをスキップしたデバイスをIGZO-TFTと呼ぶことにする。なお、気になるCBプロセスの詳細については明らかにしていない。 図10はVDs=10V印加時のIDs-VGs特性で、IGZO-TFTのSファクターは0.45Vdecから0.67V/decへ劣化。また、VGS=20VではON電流が83%に減少するとともに、Vthも-2.17Vから0.15Vへシフトした。これは、ソース/ドレインからCuがチャネルへ拡散したためと考えられる。

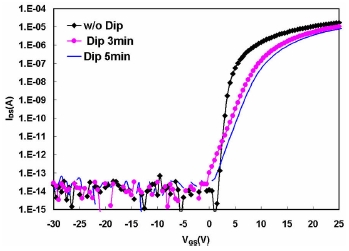

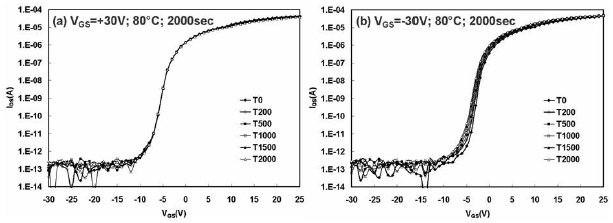

こうしたCu拡散による影響を実証するため、ゲートとソース/ドレインにAl膜を用いるとともにCuSO4(濃度0.05mol)溶液で浸漬したリファレンスデバイスを作製した。図11はそのIDs-VGs特性で、Cuが拡散すると特性が劣化することがわかる。 図12はデバイスを80℃に加熱しゲートに+30V、-30Vのバイアスストレスを2000秒印加したバイアスストレステスト結果で、CB-IGZO TFTのVthは+30V印加時で0.07V、-30V印加時で1.01Vシフトしたに過ぎなかった。 IGZO-TFTに強力なライバルが出現 a-IGZO以外の酸化物TFTでは、なんといってもソニーのIGO(In-Ga-O)TFTが注目を集めた。結論から先にいうと、そのイニシャル特性・安定性ともa-IGZO-TFTをしのぐレベルで、“酸化物TFT=a-IGZO-TFT”というこれまでの常識を覆す可能性すら感じさせた。

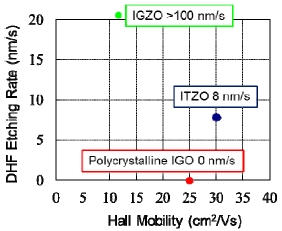

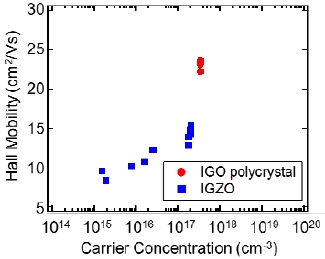

周知のように、IGZO中のZnはIn2O3の結晶化を抑制する役割、Gaはその強い結合エネルギーによってOを安定化させる役割を果たす。このため、ZnレスのIGOは信頼性が高く安定な多結晶半導体になると予想した。 具体的にはa-IGZOに比べ、①多結晶なのでHF処理でもエッチングされない、②ホールモビリティが高くプロセスマージンも広い、というメリットがある。図13はキャリア密度とホールモビリティの関係で、a-IGZOは成膜時のO2分圧を下げるとホールモビリティが10cm2/V・sから15cm2/V・sへ増加する。一方、多結晶IGOはO2分圧をはじめとする成膜条件に関わらずa-IGZOよりも高いホールモビリティが得られる。図14はホールモビリティとDHF(0.5%)によるエッチングレートの関係で、多結晶IGOは高いモビリティを維持したままDHFに対し高い耐エッチング特性を備える。 写真2に出光興産のIGOターゲットを用いて成膜したIGO膜の上面図を示す。グレインは数百nmサイズの柱状サブグレインが連なったロッドライク構造で、そのサイズは2μm程度である。こうしたサブグレイン形状はITO(In2O3-SnO2)でも観測される。

ところで、ZnOの場合、グレインバウンダリーに欠陥があるとキャリア伝導が阻害される。このため、ZnOでは膜厚に比例してグレインサイズが減少し、結果的にホールモビリティが低下する。 これに対し、IGOは膜厚50nmでも25cm2/V・sと高いホールモビリティを維持する。これは、ZnOとIn2O3の結晶性の違いによる。つまり、ZnOはウルツ型結晶、IGOは鉄マンガン鉱型結晶であり、前者に比べ対称性が低いからである。こうした理由からIGO-TFTを有機ELDのバックプレーンに用いることにした。 試作デバイスはエッチングストッパー付きボトムゲート構造を採用。しかし、図15-(a)のようにスタンダードプロセスは工程数が多く、デバイスをローコストで製造するのが難しい。そこで、図15-(b)のようにSiO2膜をエッチングストッパーとゲート絶縁膜に用いてBHFで一括エッチングし、エッチングストッパーとゲートコンタクトホールを一括パターニングすることにした。いうまでもなく、このプロセスはIGOに高い耐エッチング性があるから適用できるわけである。ちなみに、a-Si TFTでスタンダードとなっているバックチャネル構造デバイスも作製したが、エッチングストッパーレスのため、信頼性、ユニフォミティともディスプレイ用TFTとしては不十分だった。

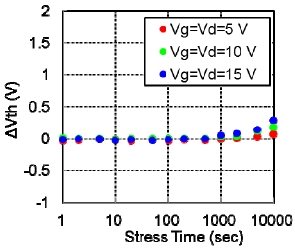

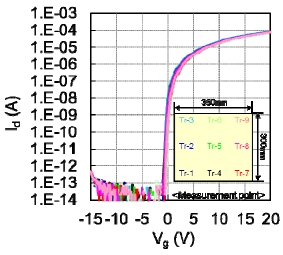

図16は第1世代マザーガラス(300×350mm)上に作製したIGO-TFTのトランスファー特性で、モビリティは23.8cm2/V・s、Vthは-0.1V、Sファクターは0.30V/decだった。また、マザーガラス全域におけるモビリティ均一性は±0.86cm2/V・sだった。 図17は50℃でVg=5~15V、Vd=5~15Vを1万秒印加したポジティブバイアスストレステスト結果で、Vthシフトはわずか0.3Vに過ぎなかった。こうした結果は、プロセス中でチャネルとソース/ドレインのコンタクト領域で大きなダメージがないためと考えられる。 写真3はIGO-TFT駆動9.9型有機ELD(960×540画素)の表示例で、シンプルな2TFT+1キャパシタ構成で駆動させることができた。

参考文献

|

||||||||||||||||||||||||||||||||||||||||||||

| REMARK 1)Stella通信はFPD&PCB関連ニュースの無償提供コーナーです(ステラ・コーポレーションがFPDやPCBそのものを製品化しているわけではありません)。 2)この記事はステラ・コーポレーション 電子メディア部が取材して記事化したものです。 |