|

STELLA捠怣偼噴僗僥儔丒僐乕億儗乕僔儑儞偑塣塩偟偰偄傑偡丅 |

IDW'08 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

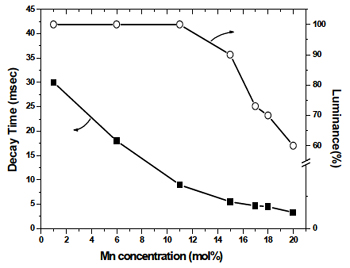

丂08擭12寧丄怴妰導偱奐偐傟偨乽IDW'08乿丅憤偠偰夋婜揑側敪昞偼彮側偔寛偟偰惙傝忋偑偭偨偲偼偄偊側偄偑丄IGZO-TFT傪偼偠傔偲偡傞巁壔暔敿摫懱偱偼敪昞偑憡師偓丄嬤偄彨棃幚梡壔偝傟傞偺偼娫堘偄側偄傛偆偵姶偠偨丅撈抐偲曃尒偱僩僺僢僋僗傪僺僢僋傾僢僾偡傞丅 3D PDP岦偗偵寀岝懱傪嵟揔壔 丂偙偙偵偒偰師悽戙僨傿僗僾儗僀偲偟偰擣抦偝傟偮偮偁傞3D僨傿僗僾儗僀偱偼丄Samsung SDI偑3D PDP梡偵僆僾僥傿儅僀僘偟偨寀岝懱傪曬崘偟偨丅08擭2寧偵儕儕乕僗偟偨悽奅弶偺50宆3D PDP僥儗價偵梡偄偨寀岝懱偱丄巆岝摿惈傪夵慞偡傞偲偲傕偵敪岝岠棪傕崅傔偨丅 丂偙偺3D PDP偼夋憸彂偒姺偊帪娫偱偁傞1僼儗乕儉傪廬棃偺1/2偵摉偨傞8msec偵愝掕丅塃栚梡夋憸偲嵍栚梡夋憸傪偦傟偧傟8msec偱揰摂偝偣偰3D壔偡傞丅偄傢備傞帪暘妱曽幃偱偁傞丅偙偺偨傔丄柺愊暘妱曽幃偺傛偆偵夝憸搙偑掅壓偡傞偙偲偼側偄丅傑偨丄2D傊偺愗傝懼偊傕梕堈偲偄偭偨傾僪僶儞僥乕僕傕偁傞丅偙偺曽幃偱3D壔偡傞偵偼丄僋儘僗僩乕僋杊巭傗嵍栚夋憸偲塃栚夋憸偺僆乕僶乕儔僢僾杊巭偺偨傔丄寀岝懱偺巆岝帪娫傪抁偔偡傞昁梫偑偁傝丄偱偒傟偽2msec偑朷傑偟偄丅偟偐偟丄昞1偺傛偆偵婛懚偺寀岝懱偼巆岝帪娫偑挿偔丄惵怓寀岝懱偱偁傞BAM(BaMgAl10O17:Eu2亄)埲奜丄3D PDP偵偦偺傑傑揔梡偡傞偙偲偼偱偒側偄丅偦偙偱丄愒怓寀岝懱偲椢怓寀岝懱傪夵椙偟偨丅

丂傑偢偼椢怓寀岝懱偩偑丄尰嵼偍傕偵梡偄傜傟偰偄傞ZnSiO4:Mn偺応崌丄恾1偺傛偆偵僪乕僷儞僩偱偁傞Mn娷桳斾棪傪崅傔傞偵偲傕側偭偰巆岝帪娫偑抁偔側傞丅偟偐偟丄偙傟偵偲傕側偭偰敪岝婸搙偼掅

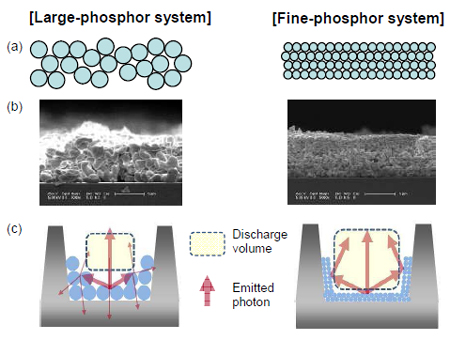

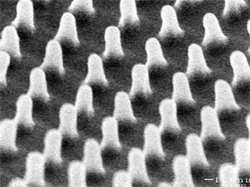

壓偡傞丅偮傑傝丄巆岝摿惈偲婸搙偼僩儗乕僪僆僼偺娭學偵偁傞丅恾1偱憃曽偑椉棫偡傞偺偼5msec偩偑丄偙傟偱傕3D PDP偵偼晄廫暘偱偁傞丅偦偙偱丄怴偨側椢怓寀岝懱偲偟偰(Y,Gd)Al3(BO3)4:Tb3亄偲Y3Al5O12:Ce3亄傪専摙偟偨丅昞2偺傛偆偵丄(Y,Gd)Al3(BO3)4:Tb3亄偼5msec丄Y3Al5O12:Ce3亄偼1msec埲壓偲偄偆巆岝帪娫偑摼傜傟傞丅摿昅偝傟傞偺偼丄偳偪傜傕147nm偱椼婲偟偨僷僂僟乕忬懺偱偼敪岝婸搙偑儕僼傽儗儞僗偱偁傞ZnSiO4:Mn偵斾傋掅偄偺偵懳偟丄僷僱儖偵寀岝枌偲偟偰揾晍偟偨応崌丄儕僼傽儗儞僗傛傝傕婸搙偑傾僢僾偡傞偙偲偱偁傞丅徻嵶側儊僇僯僘儉偼柧傜偐偵側偭偰偄側偄偑丄椙岲側婸搙朞榓摿惈傪桳偟偰偄傞偨傔偲峫偊傜傟傞丅 丂堦曽丄愒怓寀岝懱偼(Y,Gd)BO3:Eu3亄傗Y(V,P)O4:Eu3亄偑梡偄傜傟偰偄傞偑丄慜幰偼巆岝帪娫偑8.5nmsec偲挿偄丅屻幰傕巆岝帪娫偙偦4msec偲抁偄傕偺偺丄婸搙偑晄廫暘偱偁傞丅偦偙偱丄(Y,Gd)2O3:Eu3亄偺慻惉傪嵟揔壔偟丄巆岝摿惈傪3.4msec偵夵慞丅婸搙傕廬棃寀岝懱偵斾傋8亾尭偵梷惂偡傞偙偲偵惉岟偟偨丅 丂傑偨丄岠棪夵慞傪恾傞偨傔丄3怓偲傕寀岝懱僷僂僟乕傪僼傽僀儞壔偟偨丅僼傽僀儞壔偵傛偭偰僙儖撪偺寀岝枌枾搙偑岦忋偟寀岝懱敪岝偺庢傝弌偟岠棪偑岦忋偡傞偲偲傕偵丄曻揹嬻娫偑憹戝偡傞偨傔偱偁傞丅嬶懱揑偵偼丄昞3偺傛偆偵棻宎傪2.5兪m埲壓偵旝嵶壔偟偨丅愒怓寀岝懱傪儁乕僗僩壔偟桿揹懱憌忋偵僗僋儕乕儞報嶞偟偨偲偙傠丄廬棃僒僀僘僷僂僟乕偵斾傋Y(V,P)O4:Eu3亄偱9亾丄(Y,Gd)BO3:Eu3亄)偱15亾婸搙偑岦忋偟偨丅偝傜偵丄寀岝懱儁乕僗僩拞偺寀岝懱娷桳検偼摨堦側偑傜枌岤偑30亾尭彮偟偨丅偙傟傜偺寢壥丄50宆僷僱儖偱偼15乣20亾敪岝岠棪偑岦忋偟偨丅 僫僲僺儔乕傾儗僀傪愝偗偰桳婡EL偺婸搙傪50亾岦忋 丂桳婡EL娭楢偱偼丄Seoul National University偑EL敪岝偺岝庢傝弌偟岠棪傪崅傔傞偙偲偵僩儔僀偟偨丅婎斅乣摟柧傾僲乕僪娫偵僫僲僺儔乕傾儗僀僷僞乕儞傪愝偗傞傕偺偱丄婸搙偑1.5攞偵岦忋偡傞偲偄偆丅 丂慺巕峔憿偼恾3偺捠傝偱丄傑偢弨旛偲偟偰揹巕價乕儉昤夋朄偱僔儕僐儞惢儅僗僞乕儌乕儖僪傪嶌惢偡傞丅懕偄偰丄億儕僂儗僞儞傾僋儕儗乕僩(PUA)傪僔儕僐儞儌乕儖僪偵杽傔崬傫偱UV峝壔偝偣偨屻丄僔儕僐儞儌乕儖僪偐傜儕儕乕僗偡傞偙偲偵傛傝僫僲僀儞僾儕儞僩梡儌乕儖僪乽PUA儌乕儖僪乿傪嶌惢偡傞丅偙偺屻偑杮僾儘僙僗偱丄婎斅忋偵UV峝壔宆億儕儅乕乽NOA81乿傪揾晍丅PUA儌乕儖僪傪梡偄偰僫僲僀儞僾儕儞僩朄偱婎斅忋偵僫僲僺儔乕傾儗僀僷僞乕儞傪揮幨偟丄UV峝壔偝偣傞巇慻傒丅幨恀1偼僫僲僺儔乕傾儗僀偺SEM幨恀偱丄僺儔乕偼宎丄崅偝偲傕150nm偵愝掕偟丄300nm僺僢僠偱攝楍偟偨丅

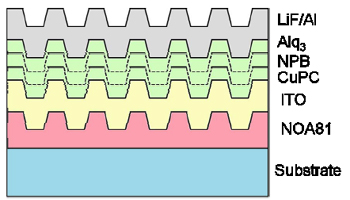

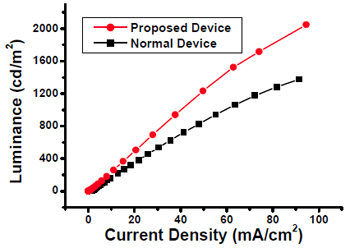

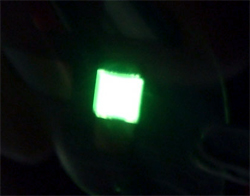

丂偙偺屻丄ITO傾僲乕僪丄CuPc儂乕儖拲擖憌丄NPB儂乕儖桝憲憌丄Alq3敪岝憌寭揹巕桝憲憌丄LiF/Al僇僜乕僪傪僐儞儀儞僔儑僫儖側僗僷僢僞朄偲忲拝朄偱愊憌惉枌偟偰慺巕傪嶌惢偟偨丅偙偙偱摿昅偝傟傞偺偼丄摟柧傾僲乕僪埲崀偺偡傋偰偺儗僀儎乕偼壓抧偱偁傞僫僲僺儔乕傾儗僀僷僞乕儞傪斀塮偟偨墯撌峔憿偵側傞偙偲丅 丂偦偺摿惈偩偑丄恾4偺傛偆偵儗僗僨僶僀僗偵斾傋婸搙偑栺50亾傾僢僾偟偨丅幨恀2偼PES僼傿儖儉忋偵嶌惢偟偨慺巕(2亊2噊)偺敪岝幨恀偱丄僫僲僺儔乕傾儗僀傪1.8亊108愝偗偨丅偙偺僥僗僩僨僶僀僗偼嬋偘偰傕敪岝忬懺偵曄壔偑側偔丄僼儗僉僔僽儖桳婡ELD偵偲偔偵桳岠偩偲偄偆丅 掅暘巕椨岝憌傪IJ朄偱宍惉 丂桳婡EL偺僾儘僙僗媄弍偱偼丄Kwangwoon Univercity偑椨岝嵽椏傪僀儞僋僕僃僢僩僾儕儞僥傿儞僌(IJ)朄偱揌壓丒僷僞乕僯儞僌偟偨掅暘巕慺巕傪曬崘偟偨丅

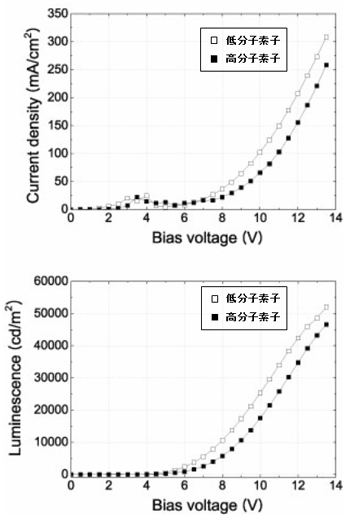

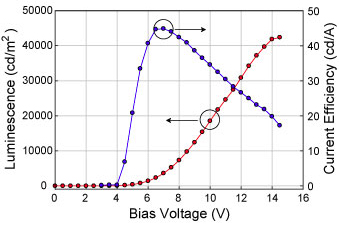

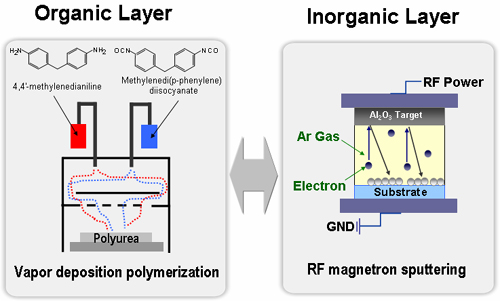

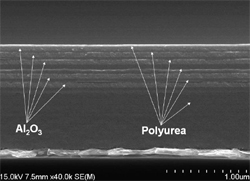

丂 IJ朄偱敪岝憌傪宍惉偡傞帋傒偼栚怴偟偔側偄偑丄掅暘巕椨岝嵽椏傪IJ朄偱宍惉偡傞揰偑What's NEW偲偄偊傞丅ITO枌晅偒僈儔僗婎斅傪UV僆僝儞張棟側偳偱昞柺張棟偟偨屻丄PEDOT/PSS儂乕儖拲擖憌傪宍惉丅偦偺忋偵椨岝敪岝僀儞僋乽EL Ink乿傪揾晍偟偨丅偙偺僀儞僋偵偼儂乕儖桝憲嵽椏丄揹巕桝憲嵽椏丄Ir(ppy)3椨岝僪乕僷儞僩偑娷傑傟偰偍傝丄1儗僀儎乕偱偙傟傜暋悢偺婡擻傪寭偹旛偊傞丅偮傑傝丄嵽椏帺懱偼掅暘巕偩偑丄峔憿偼崅暘巕慺巕偲摨偠偱偁傞丅枌岤偼80nm偱偁傞丅偙偺屻丄奐岥僷僞乕儞傪愝偗偨僔儍僪乕儅僗僋傪梡偄偰CsF(1nm)/Al(100nm)僇僜乕僪傪儅僗僋僗儖乕忲拝偟偨丅側偍丄斾妑偺偨傔丄PVK(億儕價僯儖僇儖僶僝乕儖)亄Ir(ppy)3傪巊梡偟偨崅暘巕慺巕傕嶌惢偟偨丅 丂傑偢敪岝憌傪僗僺儞僐乕僩偟偨慺巕偺摿惈傪昡壙偟偨偲偙傠丄恾5偺傛偆偵偳偪傜傕1cd/m2偺敪岝傪摼傞偺偼昁梫側揹埑偼3V偩偭偨丅偦偟偰丄掅暘巕慺巕偼4.1V偱100cd/m2丄5.3V偱1000cd/m2丄7.9V偱1枩cd/m2丄13.2V偱5枩cd/m2偺婸搙偑摼傜傟偨丅儅僢僋僗偺岠棪偼31cd/A偱丄奜晹検巕岠棪偼8.7亾偲尒愊傕傜傟傞丅僺乕僋攇挿偼510nm丄敿抣暆偼70nm偲Ir(ppy)3杮棃偺敪岝偑摼傜傟偨丅偮傑傝丄摿惈偼僐儞儀儞僔儑僫儖側PVK崅暘巕僨僶僀僗偲傎傏摨偠偩偭偨丅 丂師偵丄塼揌僒僀僘30pL偱IJ朄偵傛傝敪岝憌傪僷僞乕僯儞僌偟偨丅恾6偺傛偆偵摿惈偼僗僺儞僐乕僩慺巕偲傎傏摨偠偱丄敪岝奐巒揹埑偼3V(仐3cd/m2)丄婸搙偼7V偱3600cd/m2丄14.5V偱4枩3000cd/m2偵払偟偨丅傑偨丄儅僢僋僗偺岠棪偼7V報壛帪偺45cd/A偩偭偨丅 億儕擜慺枌偲Al2O3枌偱僴僀僽儕僢僪儗僀儎乕偱敄枌晻巭 丂桳婡ELD偺敄枌晻巭媄弍偱偼丄Samsung Electronics偑幒壏惉枌偟偨億儕擜慺廳崌枌偲Al2O3柍婡枌偺僴僀僽儕僢僪儅儖僠儗僀儎乕媄弍傪曬崘偟偨丅 丂傾儖僶僢僋偺忲拝廳崌丒僗僷僢僞憰抲偱億儕擜慺廳崌枌偲Al2O3枌傪惉枌偟偨丅慜幰偼僀僜僔傾僱乕僩儌僲儅乕偲僕傾儈儞僾儕僇乕僒傪梡偄偰埑椡0.49Pa偱嫟忲拝廳崌偟偨丅惉枌儗乕僩偼0.1兪m/min偱偁傞丅懕偄偰丄Al2O3枌傪Ar僈僗棳検42sccm丄RF僷儚乕300W丄暘埑0.29Pa偱RF僗僷僢僞儕儞僌惉枌偟偨丅枌岤偼50nm偱偁傞丅忋婰偺僾儘僙僗傪岎屳偵孞傝曉偟丄嵟廔揑偵11儗僀儎乕偵懡憌壔偟僩乕僞儖枌岤傪2兪m偵偟偨丅偙偺嵺偺壜帇岝摟夁棪偼90亾埲忋偩偭偨丅嶲峫偲偟偰幨恀3偵11儗僀儎乕晻巭枌偺抐柺幨恀傪帵偡丅

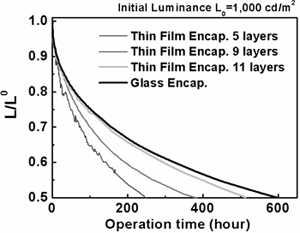

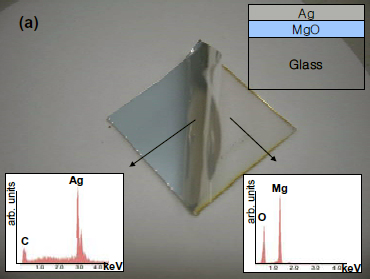

丂昞4偼堦斒揑側WVTR朄偱悈忲婥僈僗僶儕傾惈傪昡壙偟偨寢壥偱丄偄偆傑偱傕側偔儗僀儎乕悢偑憹偊傞偲僈僗僶儕傾惈傕岦忋偟丄11憌偱應掕尷奅偱偁傞5.1亊10-4g/m2/24h埲壓偑摼傜傟偨丅恾8偼2亊2噊偺掅暘巕桳婡EL僥僗僩僨僶僀僗傪婸搙1000cd/m2偱揰摂偝偣偨嵺偺婸搙敿尭庻柦偱丄11憌偺敄枌晻巭僨僶僀僗偺婸搙敿尭庻柦偼514帪娫偩偭偨丅偙傟偼丄媧幖嵻偁傝偺僈儔僗晻巭僨僶僀僗偺86亾偵摉偨傞丅傑偨丄揹棳枾搙-揹埑摿惈丄婸搙-揹埑摿惈丄岠棪-婸搙摿惈偲傕僈儔僗晻巭慺巕偲傎傏摨偠偱丄敄枌晻巭偵傛偭偰慺巕偑僟儊乕僕傪庴偗側偄偙偲偑妋擣偱偒偨丅偙偺偨傔丄11憌晻巭枌偱敄枌晻巭偟偨儃僩儉僄儈僢僔儑儞峔憿偺5.4宆掅暘巕a-Si TFT嬱摦僷僱儖(240亊300夋慺)傪嶌惢偟偨丅 MgOx攳棧憌傪梡偄偰尦僈儔僗婎斅偐傜慺巕傪儊僇僯僇儖僺乕儖僆僼 丂僼儗僉僔僽儖婎斅惢僼儗僉僔僽儖僨傿僗僾儗僀傪幚尰偡傞曽朄偲偟偰抦傜傟傞揮幨朄偱偼丄Pohang University of Science and Technology偑僼儗僉僔僽儖桳婡ELD岦偗偲偟偰MgOx攳棧憌傪梡偄偰儊僇僯僇儖偵僺乕儖僆僼偡傞傾僀僨傾傪斺業偟偨丅

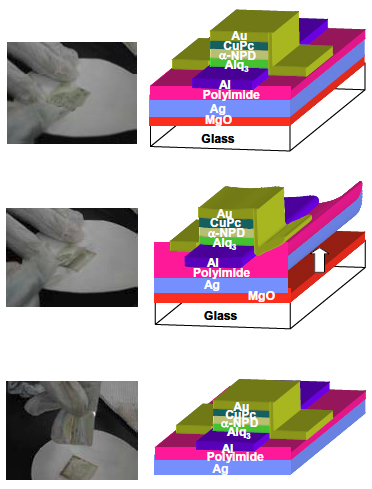

丂僼儗僉僔僽儖婎斅惢掅壏Poly-Si TFT岦偗側偳偵採埬偝傟偰偄傞廬棃偺僂僃僢僩儕僼僩僆僼朄偱偼悈暘偵庛偄桳婡ELD偵揔梡偡傞偺偑擄偟偄偨傔偱丄儐僯乕僋側儊僇僯僇儖僺乕儖僆僼朄傪峫埬偟偨丅僾儘僙僗僼儘乕偼恾9偺捠傝偱丄傑偢尦婎斅偲側傞僈儔僗婎斅偵攳棧憌偲偟偰MgOx枌傪揹巕價乕儉忲拝偡傞丅枌岤偼20nm掱搙偱偁傞丅懕偄偰丄Ag枌傪枌岤10兪m偱掞峈壛擬忲拝偟丄偝傜偵億儕僀儈僪枌傪4兪m岤偱僗僺儞僐乕僩偡傞丅偙偺寢壥丄Ag枌偺昞柺偑MgOx偲壔妛斀墳偟偰AgOx偵曄壔偡傞丅偙偺屻丄恾9偺傛偆側媡峔憿僩僢僾僄儈僢僔儑儞慺巕傪嶌惢丅嵟屻偵丄慺巕傪Ag枌懁偐傜僺乕儖僆僼偟偰尦婎斅偐傜僙僷儗乕僩偡傞丅偮傑傝丄僼儗僉僔僽儖僒僽僗僩儗乕僩偵忲拝偟偨Ag僼傿儖儉傪梡偄傞丅 丂攳棧柺傪暘愅偟偨偲偙傠丄恾10偺傛偆偵僈儔僗僒僀僪偐傜偼Mg偲O偑専弌偝傟偨丅堦曽丄Ag攳棧憌偺捈壓偱専弌偝傟偨偺偼Ag偑傎偲傫偳偩偭偨丅偙傟偼丄僺乕儖僆僼偑Ag偲MgOx偺奅柺偱敪惗偟偨偙偲傪堄枴偡傞丅Ag偲僈儔僗婎斅偺枾拝惈偼18gf/cm偲憡懳揑偵崅偄偺偵懳偟丄MgOx傪僈儔僗乣Ag娫偵憓擖偡傞偲枾拝惈偑1.4gf/cm偲戝暆偵掅壓偡傞偨傔偱偁傞丅偙偺寢壥丄尦婎斅偐傜慺巕傪梕堈偵僺乕儖僆僼偱偒傞丅 丂偪側傒偵丄僺乕儖僆僼慜屻偺慺巕摿惈傪昡壙偟偨偲偙傠丄僺乕儖僆僼慜偼婸搙偑1050cd/m2丄岠棪偑0.67cd/A偩偭偨丅偙傟偵懳偟丄僺乕儖僆僼屻偼婸搙偑980cd/m2丄岠棪偑0.59cd/A偲庒姳掅壓偟偨丅 僼儖僼儗僉僔僽儖桳婡EL岦偗偵儐僯乕僋側僾儘億乕僓儖偑 丂堦曽丄Korea Advanced Institute of Science and Technology偼僼儗僉僔僽儖桳婡EL岦偗偲偟偰儐僯乕僋側僨僶僀僗峔憿傪採埬偟偨丅偦偺栚揑偼丄姫暔傛偆側僼儖僼儗僉僔僽儖桳婡EL傪幚尰偡傞偙偲偵偁傞丅

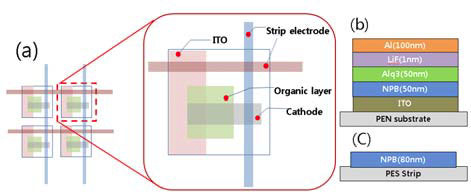

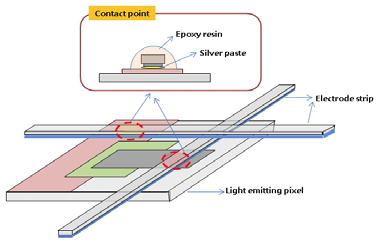

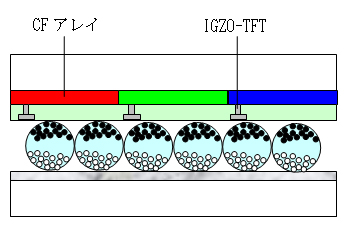

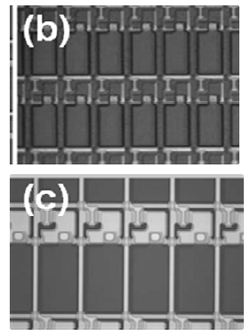

丂恾11偼僨僶僀僗峔憿偱丄ITO傾僲乕僪夋慺揹嬌丄桳婡EL憌丄Al僇僜乕僪傪偦傟偧傟僐僱僋僩偝偣側偑傜埵抲傪偢傜偡偲偲傕偵丄懷忬揹嬌傪愝偗傞丅恾11-(b)偼桳婡EL慺巕偺抐柺恾偱丄ITO傾僲乕僪/NPB儂乕儖桝憲憌/Alq3敪岝憌/LiF僶僢僼傽憌/Al僇僜乕僪偲廬棃偲摨偠偩偑丄慜婰偺傛偆偵XY偺埵抲娭學傪偢傜偟偰攝抲偡傞丅堦曽丄(c)偺傛偆偵懷忬揹嬌偼傑偢懷忬偺PES僼傿儖儉忋偵Al揹嬌傪枌岤80nm偱忲拝丅師偵丄恾12偺傛偆偵Ag儁乕僗僩偍傛傃僄億僉僔庽帀偵傛偭偰ITO傾僲乕僪夋慺揹嬌偍傛傃Al僇僜乕僪椞堟偲僐儞僞僋僩偝偣傞丅偮傑傝丄慺巕偲懷忬揹嬌偼暿乆偺僼傿儖儉忋偵嶌惢偟偨屻丄僐儞僞僋僩偝偣傞巇慻傒丅偙偺寢壥丄幨恀4偺傛偆偵嬋偘偑帺嵼側僼儖僼儗僉僔僽儖桳婡EL偑幚尰偡傞丅偄偆傑偱傕側偔丄偦偺僼儗僉僔價儕僥傿惈偼懷忬揹嬌偺暆偲攝抲僺僢僠偵傛偭偰寛傑傞丅 丂偦偺僨僶僀僗峔憿偐傜奐岥棪偑偒傢傔偰掅偄偺偵壛偊丄夝憸搙傪崅傔傞偺傕崲擄側偨傔丄僨傿僗僾儗僀偵偡傞偺偼擄偟偄偑丄僂僃傾儔僽儖傕壜擻側僼儖僼儗僉僔僽儖桳婡EL僨僶僀僗偺幚尰偲偄偆堄枴偱偼儐僯乕僋偵姶偠偨丅 IGZO偺儊儕僢僩傪嵟戝尷偵妶偐偡偨傔丄慜柺CF婎斅忋偵TFT傪 丂嬤擭丄僼儗僉僔僽儖僨傿僗僾儗僀偺傾僋僥傿僽慺巕偲偟偰夆慠拲栚搙偑忋偑偭偰偒偨巁壔暔敿摫懱丅搶嫗岺嬈戝妛偺嵶栰廏梇嫵庼傜偑敪孈偟偨傾儌儖僼傽僗IGZO(a-In-Ga-ZnO)偑戙昞揑偱丄崱夞丄撌斉報嶞偼IGZO-TFT偺摿挜傪嵟戝尷偵妶偐偟偨僼儘儞僩僪儔僀僽宆偺儅僀僋儘僇僾僙儖宆僇儔乕揹婥塲摦僨傿僗僾儗僀傪敪昞偟偨丅 丂撌斉報嶞偼暷E Ink偺儅僀僋儘僇僾僙儖宆揹婥塲摦僨傿僗僾儗僀傪IGZO-TFT偱僪儔僀僽偡傞偙偲偵僩儔僀丅偡偱偵PET僼傿儖儉婎斅傪梡偄偨5.35宆僼儗僉僔僽儖揹巕儁乕僷乕傪帋嶌嵪傒丅崱夞偼IGZO-TFT傪梡偄偨儐僯乕僋側僇儔乕揹巕儁乕僷乕偱僩僺僢僋僗傪採嫙偟偨丅

丂儐僯乕僋偲偄偭偨偺偼丄恾13偺傛偆偵IGZO-TFT傪慜柺僇儔乕僼傿儖僞乕(CF)婎斅忋偵愝偗傞偨傔丅廃抦偺傛偆偵丄廬棃偺僇儔乕揹巕儁乕僷乕偼攚柺婎斅懁偵TFT丄慜柺婎斅懁偵CF傪愝偗傞丅堦斒揑偵E Ink僨傿僗僾儗僀偺慜柺婎斅偵偼僾儔僗僠僢僋僼傿儖儉婎斅偑梡偄傜傟傞偨傔丄慜柺婎斅忋偺CF僷僞乕儞偲攚柺婎斅忋偺TFT傪埵抲崌傢偣偡傞偺偼梕堈偱偼側偄丅偙傟偵偼丄崟怓婄椏偲敀怓婄椏傪晻擖偟偨儅僀僋儘僇僾僙儖偑宎40乣50兪m偲斾妑揑戝偒偔丄偐偮抏椡惈傪桳偟偰偄傞偲偄偆棟桼傕偁傞丅偙偺偨傔丄偙偺峔憿偺僇儔乕揹巕儁乕僷乕傪崅曕棷傑傝偱検嶻偡傞偺偼擄偟偄丅 丂偦偙偱丄峫埬偟偨偺偑僼儘儞僩僪儔僀僽宆丅梕堈偵憐憸偱偒傞傛偆偵CF傾儗僀僷僞乕儞忋偵IGZO-TFT傪傾儔僀儊儞僩偟偰宍惉偡傞偺偼斾妑揑梕堈偱偁傝丄慜柺婎斅偲攚柺婎斅偺揬傝崌傢偣帪偵偼傾儔僀儊儞僩偑晄梫偲側傞丅偙偆偟偨峔憿偑幚尰偱偒偨偺偼丄IGZO-TFT偑摟柧偱丄偐偮CF偺懴擬惈傪戝偒偔壓夞傞幒壏偱宍惉偱偒傞偨傔丅 丂僆乕僶乕僐乕僩憌傪愝偗偨CF婎斅忋偵ITO僎乕僩丄SiON僎乕僩愨墢枌丄ITO僜乕僗/僪儗僀儞丄IGZO敿摫懱憌偲偄偆儃僩儉僎乕僩丒儃僩儉僐儞僞僋僩宆傪嶌惢丅TFT傾儗僀偺忋晹偵憌娫愨墢枌偲偟偰摟柧億儕儅乕傪揾晍偟偨屻丄ITO夋慺揹嬌傪宍惉偟偨丅帋嶌偟偨偺偼4宆QVGA僷僱儖偱丄僥僉僗僩昞帵帪偺婸搙傪崅傔傞偨傔丄夋慺偼RGBW僪僢僩峔惉偵偟偨丅僩儔儞僕僗僞偺僗儁僢僋偼儌價儕僥傿偑6cm2/Vec丄ON/OFF揹棳儗僔僆偑104丄Vth偑1.6V偲偝傎偳崅偔側偐偭偨偑丄揹巕儁乕僷乕傪僪儔僀僽偡傞偵偼廫暘側抣偑摼傜傟偨丅偨偩丄摟柧側IGZO-TFT偲偼偄偭偰傕夋柺婸搙偼庒姳掅壓偟偨丅 SAM偱昞柺僷僞乕僯儞僌偟偰IGZO敿摫懱憌傪帺屓惍崌僷僞乕僯儞僌 丂僽儔僓乕岺嬈傕IGZO-TFT岦偗偱怴偨側僾儘僙僗媄弍傪敪昞丅昞柺張棟媄弍傪懡梡偡傞偙偲偵傛偭偰IGZO敿摫懱憌傪帺屓惍崌揑偵僷僞乕僯儞僌偱偒傞偙偲傪帵偟偨丅

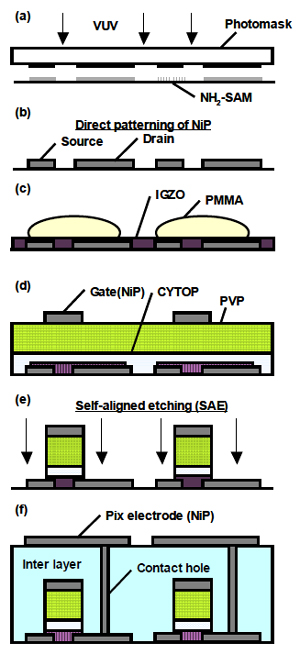

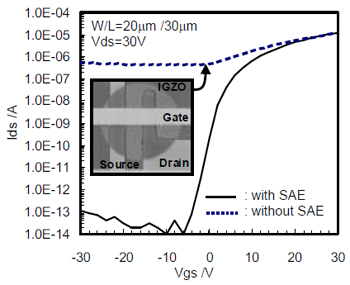

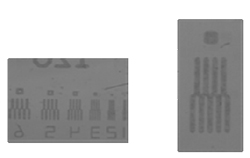

丂僾儘僙僗僼儘乕偼恾14偺捠傝偱丄傑偢婎斅傪1mol亾偺NH2張棟SAM(self assembled monolayers)梟塼拞偵怹捫偡傞丅師偵丄僼僅僩儅僗僋傪夘偟偰172nm偺UV岝傪徠幩偟偰昞柺僷僞乕僯儞僌傪峴偆丅偡傞偲丄UV徠幩偝傟偨晹暘偼NH2婎偑暘夝偝傟偰OH婎偵曄壔偡傞丅偙偺寢壥丄婎斅昞柺偑NH2晹暘偲OH晹暘偵僷僞乕僯儞僌偝傟傞丅懕偄偰丄NiP枌傪揹夝儊僢僉惉枌偡傞丅偡傞偲丄NH2晹暘偩偗偵慖戰揑偵NiP偑晅拝偟僜乕僗/僪儗僀儞揹嬌偑宍惉偝傟傞丅 丂師偵IGZO枌傪DC僗僷僢僞儕儞僌惉枌偟偨屻丄PMMA傪IJ朄偱儔僼偵僷僞乕僯儞僌丅偙偺PMMA僷僞乕儞傪儅僗僋偵偟偰IGZO枌傪僄僢僠儞僌偡傞丅 丂懕偄偰丄僼僢慺宯億儕儅乕乽CYTOP乿偲PVP(億儕價僯儖僼僃僲乕儖)傪僗僺儞僐乕僩偟偰僎乕僩愨墢枌傪宍惉偡傞丅僩乕僞儖枌岤偼800nm偱偁傞丅師偵丄忋婰偺昞柺僷僞乕僯儞僌媄弍傪梡偄偰NiP僎乕僩揹嬌傪宍惉偡傞丅偙偺屻丄僎乕僩傪儅僗僋偵偟偰僟僽儖儗僀儎乕僎乕僩愨墢枌偲IGZO枌傪僄僢僠儞僌偟偰僷僞乕僯儞僌偡傞丅偙偺寢壥丄僠儍僱儖偑帺屓惍崌揑偵僷僞乕僯儞僌偝傟傞丅 丂師偵丄僔儘僉僒儞億儕儅乕傪僗僺儞僐乕僩偟偰憌娫愨墢枌傪宍惉偟偨屻丄僐儞儀儞僔儑僫儖側僼僅僩儕僜偱僐儞僞僋僩儂乕儖傪宍惉偡傞丅嵟屻偵丄忋婰偟偨昞柺僷僞乕僯儞僌媄弍傪梡偄偰嵞搙NiP傪夋慺揹嬌偲偟偰儊僢僉丒僷僞乕僯儞僌偡傞丅偙偺寢壥丄僼僅僩儅僗僋枃悢傪4枃偵嶍尭丅偝傜偵丄SAM偺僷僞乕僯儞僌傕怹捫乣UV業岝偲2岺掱偲岺掱悢傪抁弅偡傞偙偲偑偱偒傞丅嶲峫偲偟偰丄幨恀6偵NiP僜乕僗/僪儗僀儞(慄暆10兪m)偺SEM幨恀傪帵偡丅 丂恾15偼僩儔儞僕僗僞摿惈偱丄儌價儕僥傿偼13.1cm2/Vec丄ON/OFF揹棳儗僔僆偼108丄Vth偼3.2V偲崅偄摿惈偑摼傜傟偨丅斾妑偺偨傔丄帺屓惍崌僾儘僙僗媄弍(恾15偺e偺岺掱)儗僗偺僨僶僀僗偼僜乕僗乣僪儗僀儞娫偺儕乕僋揹棳偑懡偔側傝丄恾15偺傛偆偵僆僼揹棳偑戝暆偵憹戝偟偨丅傑偨丄DC僶僀傾僗傪報壛偟偰嬱摦埨掕惈傪昡壙偟偨偲偙傠丄1000昩屻偺Vth僔僼僩偼0.8V偩偭偨丅偙傟偼丄僐儞儀儞僔儑僫儖側a-Si TFT偵旵揋偡傞丅 丂偙偺IGZO-TFT偱夝憸搙127ppi偺億儕儅乕僱僢僩儚乕僋LCD傪僪儔僀僽丅FPD偺傾僋僥傿僽慺巕偵揔梡壜擻側偙偲傪幚徹偟偨丅 僼儗僉僔僽儖桳婡EL岦偗偲偟偰怴偨側巁壔暔敿摫懱傕 丂堦曽丄ETRI偼僆儕僕僫儖慻惉偺Al2O3-ZnO-SnO2(AZTO)傪梡偄偨傾儌儖僼傽僗巁壔暔TFT傪曬崘偟偨丅 丂巁壔暔敿摫懱偲偟偰AZTO傪慖戰偟偨偺偼壔妛揑偵埨掕偱丄偐偮戝宆壔懳墳偑梕堈側僗僷僢僞儕儞僌朄偱幒壏惉枌偱偒傞偨傔丅偦偺摿惈傪昡壙偡傞偨傔丄儃僩儉僎乕僩峔憿偲僩僢僾僎乕僩峔憿偺TFT傪帋嶌偟偨丅僎乕僩偲僜乕僗/僪儗僀儞偵偼ITO傪僗僷僢僞儕儞僌惉枌丅僎乕僩愨墢枌偼Al2O3枌傪ALD(Atomic Layer Deposition)朄偵傛偭偰婎斅壏搙150亷偱惉枌偟偨丅AZTO妶惈壔憌偼Al2O3-ZnO僞乕僎僢僩偲SnO2僞乕僎僢僩傪梡偄偰嫟僗僷僢僞儕儞僌惉枌偟偨丅傕偪傠傫丄婎斅壏搙偼幒壏偱偁傞丅僠儍僱儖挿偼20兪m丄僠儍僱儖暆偼40兪m偱丄奺儗僀儎乕偲傕僐儞儀儞僔儑僫儖側僼僅僩儕僜亄僄僢僠儞僌朄偱僷僞乕僯儞僌偟偨丅

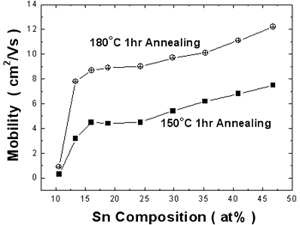

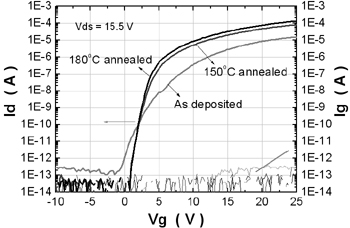

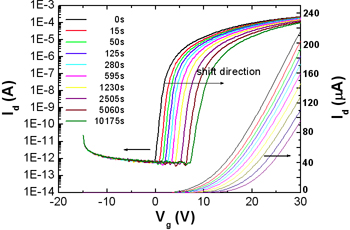

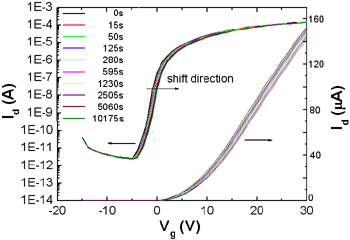

丂慜婰偺傛偆偵AZTO偼傾儌儖僼傽僗峔憿偺偨傔丄僌儗僀儞僶僂儞僟儕乕偑側偔丄戝宆婎斅柺撪偱傕嬒堦偱埨掕惈偑崅偄偺偑摿挜丅恾16偼恀嬻拞偱傾僯乕儖偟偨嵺偺僩儔儞僕僗僞摿惈偱丄傾僯乕儖儗僗僨僶僀僗偼儌價儕僥傿偑1.9cm2/Vec丄Vth偑亅2V丄ON/OFF揹棳儗僔僆偑107偩偭偨丅堦曽丄150亷偱傾僯乕儖偡傞偲儌價儕僥傿偼6.2cm2/Vec丄Vth偼0.9V丄ON/OFF儗僔僆偼109偵夵慞偝傟偨丅傑偨丄180亷偱傾僯乕儖偡傞偲儌價儕僥傿偑10.1cm2/Vec偲偝傜偵岦忋偟偨丅恾17偺傛偆偵儃僩儉僎乕僩宆偱偼Sn娷桳検偵傛偭偰儌價儕僥傿偑曄壔偟丄Sn娷桳検偑憹偊傞偵偟偨偑偭偰憹壛偟偨丅 丂恾18丄19偼250亷偱傾僯乕儖偟偨嵺偺僩僢僾僎乕僩TFT偲儃僩儉僎乕僩TFT偺僩儔儞僕僗僞摿惈偱丄儃僩儉僎乕僩宆偱偼Vth偑0V嬤曈偩偭偨偺偵懳偟丄僩僢僾僎乕僩宆偱偼亅5V偵僔僼僩偟偨丅堦曽丄儌價儕僥傿偼儃僩儉僎乕僩宆偑10.3cm2/Vec丄僩僢僾僎乕僩宆偑6cm2/Vec偩偭偨丅慜婰偺傛偆偵丄僎乕僩愨墢枌偼僩儕儊僠儖傾儖儈僯僂儉僈僗傪梡偄偰悈忲婥傪僪乕僾偟偰ALD惉枌偡傞丅偙偺偨傔丄僩僢僾僎乕僩宆偱偼僎乕僩愨墢枌偲妶惈憌偺奅柺偵悈慺偵婲場偡傞寚娮偑懡悢敪惗偡傞丅偙傟偑儌價儕僥傿偺掅壓傪傕偨傜偡偲峫偊傜傟傞丅堦曽丄僎乕僩僶僀傾僗埨掕惈偼僩僢僾僎乕僩宆偺曽偑戝暆偵崅偐偭偨丅偙傟偼丄儃僩儉僎乕僩宆偱偼AZTO枌偺僗僷僢僞惉枌偵傛偭偰僎乕僩愨墢枌偑僟儊乕僕傪庴偗丄僎乕僩愨墢枌偲妶惈憌偺奅柺偱僉儍儕傾僩儔僢僾僒僀僩偑懡偔偱偒傞偨傔偲峫偊傜傟傞丅偙傟傜偐傜丄桳婡ELD偺傾僋僥傿僽慺巕偲偟偰偼僩僢僾僎乕僩宆偑朷傑偟偄偲敾抐偟偨丅

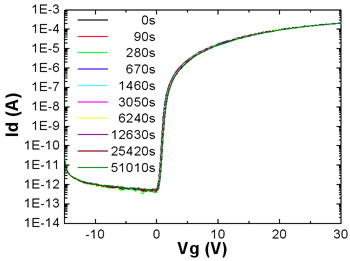

丂偦偙偱丄僩僢僾僎乕僩宆偵偍偗傞慜婰偺ALD惉枌帪偺栤戣傪夝寛偡傞偨傔丄A2O3僎乕僩愨墢枌傪ALD惉枌偡傞慜偵AZTO枌忋偵A2O3曐岇枌傪僾儔僘儅ALD朄偱惉枌偟偨丅偙傟偼丄悈慺偵傛傞妶惈憌偲僎乕僩愨墢枌偺奅柺寚娮傪梷惂偡傞偨傔丅枌岤偼40nnm偱偁傞丅偙偺寢壥丄儌價儕僥傿傪儃僩儉僎乕僩宆暲傒偺9.5cm2/Vec偵崅傔偨丅恾20偼摦嶌埨掕惈傪帵偟偨傕偺偱丄僎乕僩揹埑亄20V傪報壛偟偨14帪娫屻偱傕Vth僔僼僩偼傢偢偐0.2V偩偭偨丅偙偺僩僢僾僎乕僩宆AZTO-TFT傪梡偄偰3.5宆惵怓儌僲僇儔乕桳婡EL(176亊220僪僢僩)傪僪儔僀僽偡傞偙偲偵惉岟偟偨丅 丂億僗僩ITO偲偄偆娤揰偱偼丄CNT(僇乕儃儞僫僲僠儏乕僽)傪摟柧摫揹枌偵梡偄傞採埬偑憡師偄偩丅暷崙偺CNT僀儞僋儊乕僇乕丄Unidym偼Samsung Electronics偲CNT僐儌儞揹嬌傪梡偄偨僼儗僉僔僽儖傾僋僥傿僽嬱摦儅僀僋儘僇僾僙儖宆揹婥塲摦僨傿僗僾儗僀傪敪昞丅偝傜偵丄Si-Display Tech偲嫟摨偱僐儌儞揹嬌偲夋慺揹嬌偵CNT傪梡偄偨5.5宆a-Si TFT-LCD傪曬崘偟偨丅

丂屻幰偩偑丄擬CVD朄偱崌惉偟偨CNT傪僗儕僢僩僐乕僩岦偗偲偟偰僀儞僋壔偟偨屻丄CF婎斅偍傛傃TFT婎斅偵僗儕僢僩僐乕僩偟幒壏偱姡憞偝偣偨丅枌偺壜帇岝摟夁棪偼85亾埲忋偱偁傞丅夋慺揹嬌岦偗偱偼僼僅僩儕僜亄O2僪儔僀僄僢僠儞僌偱僷僞乕僯儞僌偟偨丅C(枌)亄O2(僈僗)仺CO2(僈僗)偲偄偆儊僇僯僘儉偱丄僄僢僠儞僌巆熢偼側偄丅傑偨丄僪儔僀僄僢僠儞僌儗乕僩傕偒傢傔偰懍偄丅嶲峫偲偟偰幨恀7偵3兪m暆偱僷僞乕僯儞僌偟偨CNT僷僞乕儞丄幨恀8偵幚嵺偺TFT傾儗僀(僼僅僩儗僕僗僩尰憸屻偲僪儔僀僄僢僠儞僌乣儗僕僗僩攳棧屻)傪帵偡丅夋慺揹嬌娫偺僊儍僢僾偼10兪m偱偁傞丅偪側傒偵丄CNT枌偼僂僃僢僩僄僢僠儞僌朄傗儗乕僓乕僟僀儗僋僩僄僢僠儞僌朄 偱傕僷僞乕僯儞僌偱偒傞丅 丂僐儌儞揹嬌丄夋慺揹嬌偲傕僐儞儀儞僔儑僫儖側ITO/IZO偵斾傋偨嵺偺儊儕僢僩偼僼儗僉僔僽儖懳墳偑梕堈偱丄僂僃僢僩僐乕僩朄偱惉枌偡傞偨傔僗僥僢僾僇僶儗僢僕惈偑崅偄偙偲丅幚嵺丄CF婎斅忋偺僐儌儞揹嬌偱偼RGB拝怓憌僷僞乕儞偺忋偵暯妸壔憌偑晄梫偵側傞丅 丂堦曽丄TFT偺夋慺揹嬌偲偟偰梡偄傞応崌丄僐儞僞僋僩儂乕儖偲僪儔僀僶IC幚憰僷僢僪椞堟傪僇僶乕偡傞昁梫偑偁傞丅僐儞僞僋僩儂乕儖偺堦斒揑側僨傿儊儞僕儑儞偼暆5兪m丄怺偝100乣500nm偱偁傞丅僐儞僞僋僩儂乕儖傪3乣5兪m偵愝掕偟偰CNT僀儞僋傪揾晍偟偨偲偙傠丄宎1乣2nm丄挿偝1乣5兪m偺CNT傪梡偄傞偲僪儗僀儞揹嬌偲廫暘僐儞僞僋僩偱偒傞偙偲偑傢偐偭偨丅偙偺嵺偵栤戣偲側傞愙怗掞峈傕5兪m暆僐儞僞僋僩儂乕儖偱500兌m偲廫暘彫偝偐偭偨丅 丂幨恀9偵CNT摟柧摫揹枌傪僐儌儞揹嬌偲夋慺揹嬌偵梡偄偨5.5宆VGA TFT-LCD偺昞帵椺傪帵偡丅偨偩丄僩乕僞儖摟夁棪偼ITO僨僶僀僗偵斾傋10亾掅壓偟偨丅偨偩丄偙傟偼CNT僀儞僋偺夵椙偵傛偭偰嬤偄彨棃夝寛偱偒傞偲偟偰偄傞丅 嶲峫暥專 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||