|

STELLA通信は㈱ステラ・コーポレーションが運営しています。 |

SID 11~新型TFT編 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

N2Oプラズマ処理によってa-IGZO-TFTの特性安定性を改善 酸化物TFTとして存在感を確立したアモルファスIGZO(In-Ga-Zn-O)-TFTはこれまでの発表と異なり、信頼性を追求した報告が目立った。いうまでもなく、TFT-LCDなどで量産採用が決まっているためで、今回の発表論文をみても次世代TFTとして完全に一歩リードした印象を受けた。

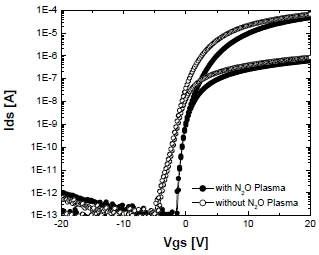

そうしたなか、LG DisplayはN2Oプラズマ処理によってa-IGZO-TFTの特性を安定化させることに成功した。周知のように、a-IGZO-TFTはとくに高照度環境下でVthシフトが大きくなる。そこで、N2Oプラズマ処理によってこうした問題を解消することにした。 実験では、エッチストッパー付きボトムゲート構造IGZO-TFTを370×470㎜マザーガラス上に作製した。ゲート絶縁膜、エッチストッパー、パッシベーションはSiO2膜をプラズマCVD成膜。活性層はInGaZnO4ターゲットを用いて室温でDCスパッタリング成膜した。ソース/ドレインにはMoメタルを使用。各レイヤーともコンベンショナルなフォトリソ技術でパターニングした。これらフォトリソプロセスで用いられる薬品はIGZO表面にダメージを与えるため、上記のようにN2Oプラズマ処理を行った。 図1は電圧-電流特性で、N2Oプラズマ処理デバイスはSファクター=0.19V/dec、Vth=0.1V、キャリアモビリティ=8.77cm2/V・sが得られた。つまり、N2Oプラズマ処理レスに比べSファクターが大幅に改善されVthシフトも小さくなった。 一般的に、酸化物半導体はTFT製造プロセスや外部環境に非常にセンシティブであるとされる。a-IGZO-TFTも例外ではなく、成膜・パターニング時にバルクレイヤーで酸素欠乏が起こる。この結果、Sファクターが大きくなり、イニシャルに比べ特性が大幅に低下する。これに対し、N2Oプラズマ処理をすると、酸素欠乏を相殺するため、Sファクターが小さくなる。

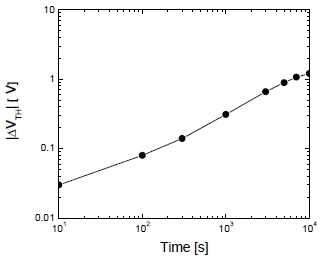

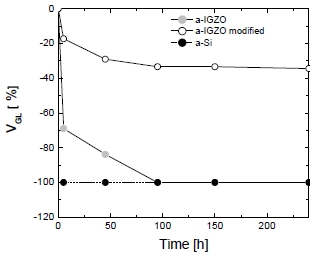

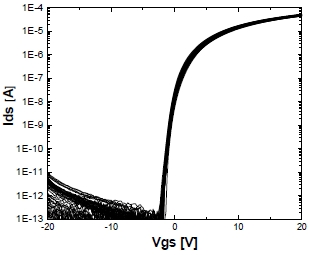

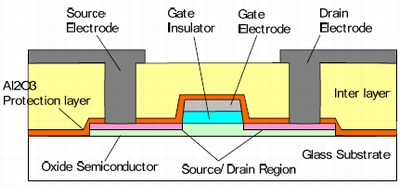

しかし、N2Oプラズマ処理を行うと、基板面内のユニフォミティは低下しやすい傾向になる。これは、a-IGZO膜やエッチストッパーの成膜条件などによって改善することができる。図2は基板面内の49個のTFTを評価した結果で、ほとんどのTFTは理想的なトランスファーカーブを示し、特性偏差もモビリティが0.29(8.26cm2/Vs)、Vthが0.18(0.85V)、Sファクターが0.07(0.23V/dec)と小さかった。これは、N2Oプラズマ処理が酸素欠乏相殺効果だけでなく、面内ユニフォミティ改善に有効なキャリア密度低減に寄与するためである。 ところで、TFTをディスプレイデバイスに用いる場合、高照度環境下における特性安定性が非常に重要となる。そこで、さまざまな条件でネガティブ&ポジティブBTSテストを行った。図3は照度環境下におけるネガティブBTSテストの結果で、1万時間後のVthシフトは-1.21Vに過ぎなかった。これは、これまでに報告されているなかで世界最高に当たる。 さらに、a-IGZO-TFT駆動17型IPSモードLCDを高温高湿環境で2か月ドライブさせたところ、図4のようにリファレンスであるa-Si TFTは特性がまったく変動しなかった。これに対し、N2Oプラズマ処理レスIGZO-TFT駆動LCDは時間の経過とともに特性が大幅に変動した。他方、N2Oプラズマ処理したIGZO-TFT駆動LCDは特性がほとんど変化せず、a-Si並みの信頼性があることが確認できた。 セルフアライントップゲートIGZO-TFTはドライバ回路もビルトイン可能 a-IGZO-TFTの製造プロセス関連では、ソニーがセルフアライン構造のソース/ドレイン領域を設けたトップゲート型デバイスを報告した。コンベンショナルなトップゲート構造では寄生容量が大きく、TFTサイズをシュリンクすることが難しいほか、応答性も低下するため。 図6は試作デバイスの断面構造で、まずa-IGZO膜をスパッタリング成膜しウェットエッチングでパターニングする。続いて、SiO2膜をプラズマCVD成膜してゲート絶縁膜を形成。次に、ゲート電極としてAl/Tiをスパッタリング成膜した後、ゲート絶縁膜とゲート電極をドライエッチングする。そして、活性層エリアにおけるソース/ドレイン領域を設けるため、Alをスパッタリング成膜し、大気中において300℃でアニールする。この結果、ソース/ドレイン領域とAl2O3保護膜が同時にできる。この後、有機パッシベーションを塗布してパターニング。最後に、Mo/Alを成膜しウェットエッチングでパターニングしてソース/ドレイン電極を形成する。

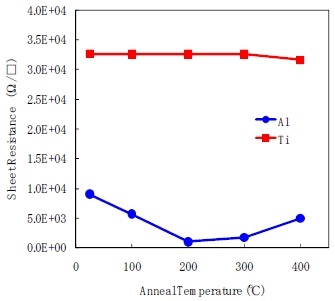

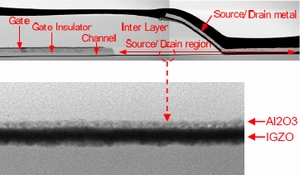

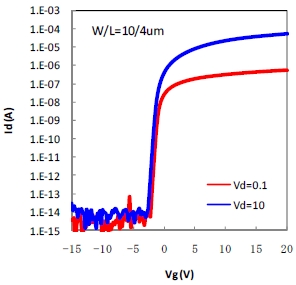

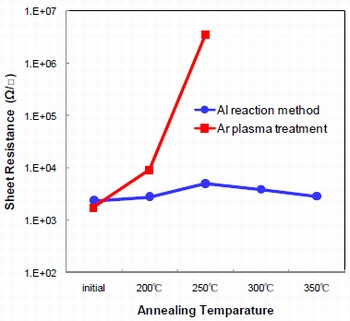

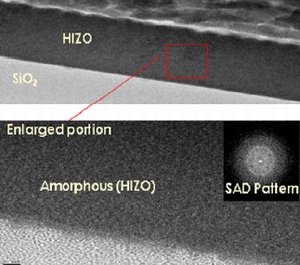

写真1は断面TEM像で、IGZO膜上に均一なAl2O3膜が形成されていることがわかる。このセルフアライントップゲート構造IGZO-TFTを有機ELDのバックプレーンに用いると、画素電極を含め計5枚のフォトマスクで作製できる。 図7はチャネル長4μm、チャネル幅10μmデバイスのトランスファー特性で、ドレイン電圧10V時でサブスレッショルドスイング=0.22V/dec、Vth=-1.5V、モビリティ=9.8cm2/V・s、ミニマムOFF電流=10fAと良好な特性が得られた。また、オーミックコンタクト性も良好だった。これらの結果は、Alリアクティブメタルによって特性が向上したためと考えられる。 ところで、有機ELD用バックプレーンには高い耐熱性が求められる。そこで、セルフアライントップゲート構造IGZO-TFTのシート抵抗値が熱処理によって変化するかを調べた。この際、リファレンスとしてArプラズマ処理によってセルフアライン構造ソース/ドレイン領域を形成したデバイスも作製した。図8にソース/ドレイン領域のシート抵抗値とアニール温度の関係を示す。Arプラズマ処理デバイスは初期値こそシート抵抗値が低かったが、アニール温度が200℃になると急激にシート抵抗値が上昇した。これに対し、今回のリアクティブメタルデバイスはアニール温度の上昇にともなうシート抵抗値の上昇はわずかでかつ緩やかだった。

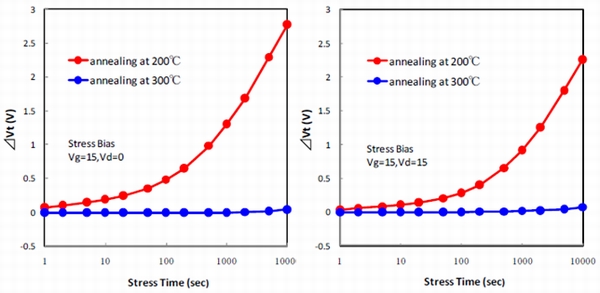

図9にVg=15V、Vd=0VとVg=15V、Vd=15Vと2種類の条件でバイアスストレスを50℃の酸素雰囲気で1万秒印加したBTS後のVthシフトを示す。どちらのケースとも200℃アニールではVthシフトが大きかったのに対し、300℃アニールではVthシフトがほとんどなかった。これは、高温アニールによってIGZO-TFTの特性が変動する要因、つまり水分、酸素、水素といった不純物が除去されたためと考えられる。

いうまでもなく有機ELDのバックプレーンに用いる場合、ピクセル用TFTの形成プロセスでガラス基板上にゲートドライバ回路やデータドライバ回路をビルトインするのが理想である。もちろん、それにはかなりのハイモビリティが要求される。これにはキャリア密度の高い酸化物半導体を用いるのが有効である。そこで、2:2:1組成ではないIGZOターゲットを用いて活性層を成膜したところ、モビリティが21.4cm2/V・sに向上。Vthも-1.6V、サブスレッショルドスイングも0.12V/decとさらなる特性改善がみられた。このため、セルフアライン構造のトップゲート型IGZO-TFTを用いれば有機EL基板上にドライバ回路をビルトインすることも可能と考えられる。 写真2にセルフアライン構造トップゲート型IGZO-TFTを用いた9.9型有機ELD(960×540画素)の表示例を示す。なお、このパネルは2:2:1組成のIGZOターゲットを使用してIGZO膜を成膜した。輝度は600cd/m2以上、コントラストは100万:1以上、色純度はNTSC比96%で、プロダクトとして十分なクオリティが得られた。 ゲート絶縁膜をポーラス状にしてモビリティを17倍に

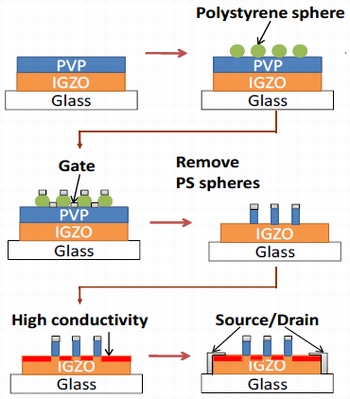

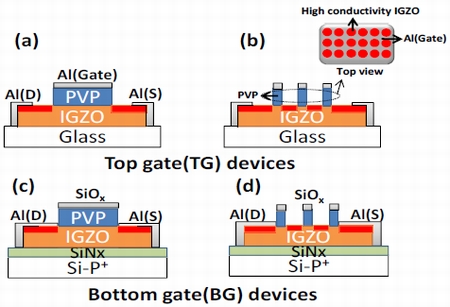

一方、National Chiao Tung University(台湾)はa-IGZOチャネル上にナノドットパターンを設けることによりキャリアモビリティを世界最高レベルに高めることに成功した。PVP(ポリビニルフェノール)ゲート絶縁膜内にナノサイズの空孔パターンを設けたもので、モビリティはコンベンショナルなレスデバイスに比べ17倍に向上した。 その効果を検証するため、実験では図10のように4種類のデバイスを作製した。ナノドットパターン付きトップゲート型デバイスのプロセスフローは図11の通りで、まずガラス基板上に径3インチのロータリー型IGZOターゲット(In:Ga:Zn=1:1:1at%)を用いてa-IGZO膜を膜厚50nmでRFスパッタリング成膜する。基板温度は室温で、RFパワーは100W、Arガス流量は30sccmである。この際、開口パターンを設けたシャドーマスクを基板上にセットすることによりマスクスルーパターニングする。この後、N2雰囲気で400℃×90分アニールする。 続いて、PVPを膜厚420nmでスピンコートし大気中で200℃×60分焼成してゲート絶縁膜を形成する。この後、出力50WでO2プラズマを照射し、PVP膜の表面を親水性に改質する。

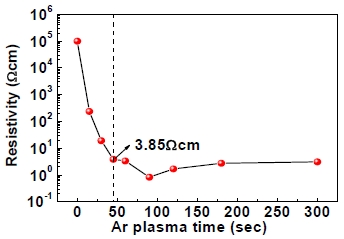

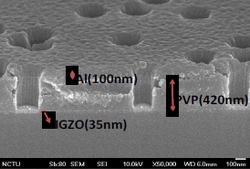

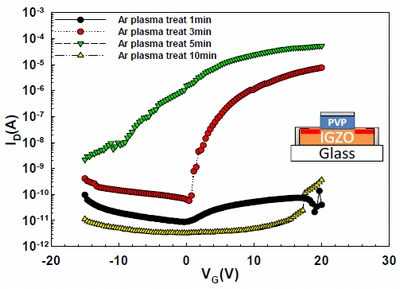

次に、Al膜を膜厚40nmで蒸着してゲート電極を形成する。続いて、接着テープによってポリスチレン粒子を基板上から除去した後、O2プラズマを出力150Wで8分照射するとAlが被覆していないPVP部分が除去される。この結果、PVPゲート絶縁膜内にポーラスなナノドットパターンができる。 この後、ソース/ドレイン領域とPVPがなく露出したチャネル領域をArプラズマ処理する。これは、ゲート領域におけるソース/ドレインメタルパッドとチャネル間の直列抵抗を低減するためである。この結果、ソース/ドレイン領域はセルフアライン構造となる。 最後に、Al膜を膜厚100nmでマスクスルー蒸着してソース/ドレインを形成する。写真3にチャネル長500μm、チャネル幅3000μmデバイスの断面SEM像を示す。なお、リファレンスであるナノドットパターンレスデバイスはポリスチレン粒子付着・除去工程を除き同じフローで作製した。 他方、ボトムゲート型デバイスはガラスに代わって基板に膜厚100nmのSiNx膜付きシリコンウェハーを使用するとともに、Alゲートに代わって膜厚40nmの熱酸化SiOxを用いた。これ以外のフローはトップゲート型デバイスと同じである。 図12はArプラズマ照射時間とa-IGZO膜の比抵抗の関係で、Arプラズマ処理によって比抵抗は105Ω・cmクラスから3.85Ω/□と劇的に低下した。これは、アズデポa-IGZO膜は酸素欠乏によって化学量論組成に比べ組成比がずれるのに対し、Arプラズマ処理を行うとa-IGZO膜の電子キャリア濃度が急激に増えるためである。

図13はナノドットパターンレスのトップゲート型デバイスにおけるArプラズマ処理時間とI-V特性の関係で、照射時間を3分にするともっとも良好な結果が得られた。一方、処理時間が5分以上になるとIGZO膜とPVP膜がダメージを受けるため、I-V特性が低下した。 表2はトップゲート型デバイスのトランスファー特性で、ナノドットパターンを設けると特性が大幅に向上し、ポリスチレン0.8wt%でモビリティは79cm2/V・sに達した。つまり、ナノドットパターンを設けるだけでモビリティは17倍も向上したわけである。周知のように、これまで報告されているa-IGZO酸化物半導体のモビリティはほとんどが35cm2/V・s以下である。ただし、high-kゲート絶縁膜を使ったデバイスでは62cm2/V・s、マルチレイヤー絶縁膜を使ったデバイスでは124cm2/V・sが報告されており、これらを考えても今回の値は世界最高クラスといえる。ここでナノドットパターンは、活性層内で無数の超微細チャネルができる結果、チャネル領域の電界特性を改善すると説明できる。これは、デュアルゲート構造の電界効果トランジスタでも同様の説明がされている。しかし、デュアルゲート構造が3倍しかモビリティが向上しなかったことを考えると、今回の結果は驚異的といえる。 表3はボトムゲート型デバイスの特性で、トップゲート型ほどの特性向上はみられなかった。そのメカニズムについてはまだ解明できていないが、それでもモビリティは2倍にアップした。 HfInZnO-TFTのポテンシャルはIGZO-TFT以上?

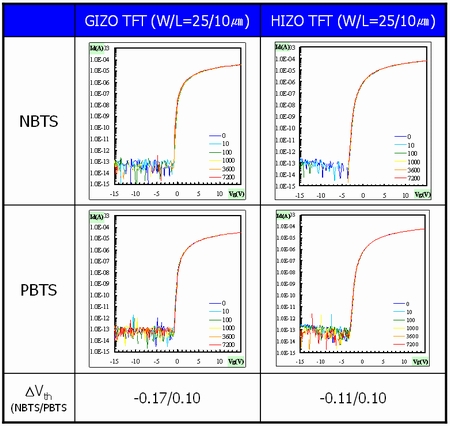

IGZO-TFT以外の酸化物TFTでは、Samsung Mobile DisplayがアモルファスHfInZnO-TFT(a-HIZO)を提案。モビリティをIGZO-TFT並みに高め、14型有機ELDをドライブしたことを報告した。 今回の研究では、370×470㎜マザーガラスを用いてエッチングストッパー付きボトムゲート構造デバイスを作製した。チャネル長は25μm、チャネル幅は10μmである。 製造フローは、まずMo膜を膜厚200nmで成膜しフォトリソでパターニングしてゲート電極を形成。続いて、SiOx膜を膜厚200nmでプラズマCVD成膜しゲート絶縁膜を形成する。この後、HfInZnOターゲットを用いてa-HIZO膜を膜厚50nmで室温スパッタリング成膜する。Ar/O2ガス混合比は72:28で、投入パワーは1.2kWである。写真4はHIZO膜とSiO2膜の界面近傍のTEM像で、HIZO膜にはマイクロストラクチャーのような結晶構造がみられず、均一なアモルファス状態になっていることがわかる。 a-HIZO膜をフォトリソ+ウェットエッチングでパターニングした後、膜厚200nmでエッチングストッパー膜をプラズマCVD成膜しフォトリソでパターニングした。次に、Mo膜を300nmでスパッタリング成膜しフォトリソ+ドライエッチングでパターニングしソース/ドレインを形成。最後に、250℃×1時間アニールした。 デバイス面内9か所の特性を測定したところ、モビリティは10cm2/V・s、ON/OFF電流レシオは108以上、サブスレッショルドスロープは0.21V/decだった。いうまでもなく、これらはコンベンショナルなa-Si TFTをはるかにしのぐ。

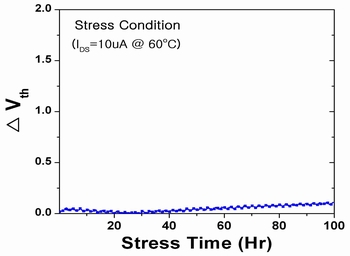

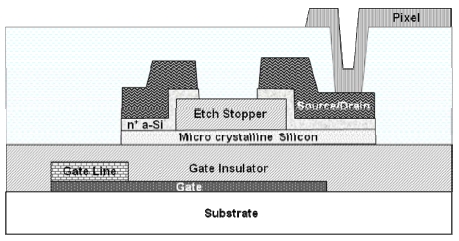

また、60℃環境でVG=-20V、VG=20Vを印加したBTSテストを行ったところ、図14のようにポジティブバイアス(PBTS)下ではVthがプラス方向に0.1V、ネガティブバイアス(NBTS)下ではネガティブ方向に0.11Vシフトした。これに対し、リファレンスとして作製したa-IGZO-TFTのVthシフトはPBTSで0.1V、NBTSで-0.17だった。つまり、アモルファス酸化物半導体のデファクトスタンダードといえるIGZO-TFTよりも信頼性が高いことがわかった。図15は60℃でIds=10μAを印加した際のVth評価結果で、過酷な環境ながら100時間後のVthシフトは0.2Vに過ぎなかった。 上記の結果を受け、a-HIZO-TFTをバックプレーンに用いたボトムエミッション型14型有機ELD(960×540画素)を試作した。ピクセル構成は3TFT-1キャパシタで、スキャンドライバ回路を基板上にビルトインした。なお、有機ELはRGB独立発光方式で、緑色発光層と赤色発光層には燐光材料、青色発光層には蛍光材料を用いた。参考として写真5に画像表示例を示す。 パターニングした光熱変換膜越しにIRレーザーを照射してa-SiをμC-Si化 a-Si TFTと低温Poly-Si TFTの中間的性質で有機ELD用アクティブ素子として有望とされるマイクロクリスタルシリコン(μC-Si)TFTでは、LG DisplayがIRレーザー結晶化技術を用いた6枚マスク製造プロセスを発表した。

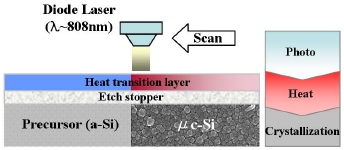

周知のように、ほとんどのメタル薄膜は大気中でIR放射波を吸収する。したがって、今回のレーザー結晶化技術ではIR放射波をメタル薄膜によって熱に変換してa-Siプリカーサを結晶化させる仕組み。ここでメタル薄膜がa-Si上だけにあれば、IRレーザー照射によってチャネル内のa-Siだけを結晶化することができる。ちなみに、IRレーザー照射プロセスはエキシマレーザーアニールをはじめとする他の結晶化法に比べ、①a-TFT製造工程におけるコンパチブル性が高い、②レーザーダイオードは実効出力が安定しており、稼働率も高い、③大型基板にも容易に対応可能、④スループットも比較的速い、といったメリットも有する。 図16にIRレーザーを用いた間接加熱結晶化プロセスのイメージを示す。波長808nmのIRレーザービームはMo光熱変換膜を通過してa-Siプリカーサに到達し、μC-Siに結晶化させる。

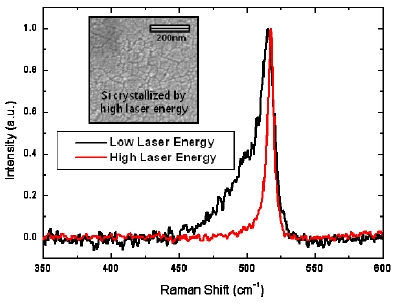

実験では370×470㎜マザーガラス(t=0.5㎜)を使用。ゲートは2パートに分かれており、通常のゲート電極にMo-Ti、ゲートバスラインにCuを用いた。これらを連続成膜した後、フォトレジストをハーフトーン露光技術によってハーフトーン露光する。つまり、ハーフトーン露光した半露光部のフォトレジストをO2アッシングによって除去し、その下部にあるCu膜をエッチングで除去してゲートライン相当部分だけにCuを残す(PEP1)。これは、導電性が高い反面、融点が低いCuをTFTのゲートパッドから離してゲートラインとして機能させ、後述するレーザー結晶化工程におけるダメージを回避するためである。 続いて、SiO2ゲート絶縁膜、 a-Si:H活性層、SiO2エッチングストッパーをプラズマ成膜する。ここでSiO2エッチストッパーは熱伝導性が低いため、Mo~Si間の反応を防ぐ機能も果たす。 次に、IRレーザーを吸収するMo光熱変換膜をパターニングする(PEP2)。IRレーザー照射プロセスによってa-Siを選択的に結晶化した後、Mo光熱変換膜をウェットエッチングによって除去する。 続いて、SiO2エッチングストッパーをパターニングする(PEP3)。この後、μC-Si膜の表面を改質した後、n+ a-Siを成膜する。そして、n+レイヤー上にMoソース/ドレインを成膜。次に、ソース/ドレインをウェットエッチング、さらに活性層とn+層を3Dフォトマスクを用いて一括でドライエッチングする(PEP4)。最後にパッシベーション(PEP5)、そして画素電極(PEP6)を形成する。 作製したμC-Siをラマンスペクトル解析したところ、515cm-1前後にピークが観察され結晶化していることが確認できた。しかし、ハイパワーでIRレーザーを照射すると、図18のようにピークはより鋭くなった。これは、Siグレインが大きくなったことを意味する。そのグレインサイズは数十nmと見積もられ、結晶化率も80%程度に達した。

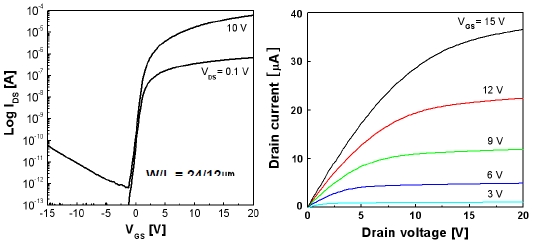

図19はチャネル長12μm、チャネル幅24μmのμc-Si TFTの特性で、平均モビリティは6.2cm2/V・sだった。いうまでもなく、電流注入型デバイスである有機ELDではドライビングTFTのON/OFF電流レシオがきわめて重要になる。今回のμc-Si TFTのON/OFFレシオは108で、有機ELDをドライブするのに十分な値が得られた。なお、その他のスペックはVthが1.46V、スレッショルドスイングが0.41V/decだった。 参考文献 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| REMARK 1)Stella通信はFPD&PCB関連ニュースの無償提供コーナーです(ステラ・コーポレーションがFPDやPCBそのものを製品化しているわけではありません)。 2)この記事はステラ・コーポレーション 電子メディア部が取材して記事化したものです。 |