FPD丄PCB丄師悽戙岝尮偺僯儏乕僗僒僀僩 STELLA捠怣 |

|

仸STELLA捠怣偼噴僗僥儔丒僐乕億儗乕僔儑儞偵傛偭偰塣塩偝傟偰偄傑偡丅 supported by Stella Corpration., Inc. |

SID 2012 |

||||||||||||||||||||||||||||

僎乕僩愨墢枌偲僷僢僔儀乕僔儑儞偵億儕儅乕傪梡偄偰僼儗僉僔僽儖壔

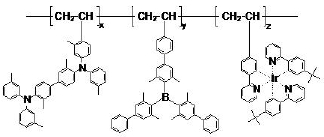

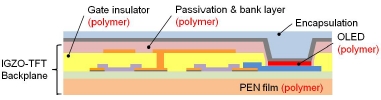

丂偙偙偵偒偰a-Si TFT丄掅壏Poly-Si TFT偵師偖戞3偺TFT偲偟偰姰慡偵僆乕僜儔僀僘偝傟偰偒偨巁壔暔TFT偱偼丄NHK曻憲媄弍尋媶強偑巁壔暔TFT偱偼斾妑揑捒偟偄僩僢僾僎乕僩峔憿偺僼儗僉僔僽儖傾儌儖僼傽僗IGZO-TFT傪帋嶌丄椨岝桳婡EL僨傿僗僾儗僀傪僪儔僀僽偟偨偙偲傪曬崘偟偨丅 丂TFT偼傕偭偲傕僔儞僾儖側2T1C峔惉傪嵦梡丅僗僀僢僠儞僌TFT偼僺僋僙儖傪慖戰丄僪儔僀僽TFT偼桳婡EL傪僪儔僀僽偡傞偨傔偵梡偄傞丅 丂恾1偵僾儘僙僗僼儘乕傪帵偡丅僒僽僗僩儗乕僩偵偼125兪m岤偺PEN僼傿儖儉傪巊梡丅傑偢愙拝嵻傪夘偟偰僉儍儕傾僈儔僗偵屌掕偡傞丅偙偺屻偑杮僾儘僙僗偱丄傑偢僶儕傾枌偲偟偰SiOx枌傪僗僷僢僞儕儞僌惉枌丅懕偄偰丄Cr(5nm)/Au(25nm)枌傪惉枌偟僼僅僩儕僜偱僷僞乕僯儞僌偟偰僜乕僗/僪儗僀儞傪宍惉偡傞丅師偵丄夋慺揹嬌偲偟偰ITO枌傪枌岤90nm偱僗僷僢僞惉枌偟僼僅僩儕僜偱僷僞乕僯儞僌偟偨屻丄O2僾儔僘儅張棟偵傛偭偰昞柺夵幙偡傞丅懕偄偰丄a-IGZO枌(30nm)傪Ar/O2暤埻婥偵偍偄偰幒壏偱僗僷僢僞惉枌偟丄僼僅僩儕僜偱僷僞乕僯儞僌偟偰巁壔暔敿摫懱憌傪宍惉丅偙偺屻丄僆儗僼傿儞億儕儅乕傪枌岤300乣400nm偱僗僺儞僐乕僩偟偰130亷偱峝壔偟偰僎乕僩愨墢枌傪宍惉偡傞丅偪側傒偵丄偙偺億儕儅乕偼媧幖惈偑掅偔丄傾僋儕儖庽帀偺傛偆側堦斒揑側桳婡愨墢嵽椏偵斾傋儕乕僋揹棳偑彮側偄偲偄偆棙揰傪桳偡傞丅嵟屻偵丄Au枌傪枌岤30乣40nm偱惉枌偟僄僢僠儞僌偟偰僎乕僩揹嬌傪宍惉偡傞丅 丂幨恀1偼嶌惢偟偨僼儗僉僔僽儖8宆a-IGZO-TFT偱丄僠儍僱儖挿偼7兪m丄僠儍僱儖暆偼僪儔僀價儞僌TFT偑35兪m丄僗僀僢僠儞僌TFT偑55兪m偱偁傞丅僺僋僙儖僺僢僠偼255兪m偱丄夝憸搙100ppi偵憡摉偡傞丅 丂恾2偼帋嶌偟偨a-IGZO-TFT嬱摦僼儗僉僔僽儖桳婡ELD偺峔憿偱丄a-IGZO-TFT宍惉屻丄傑偢僷僢僔儀乕僔儑儞偲偟偰僆儗僼傿儞億儕儅乕傪枌岤2乣3兪m偱僗僺儞僐乕僩偟僼僅僩儕僜偱僷僞乕僯儞僌偡傞丅偙偺億儕儅乕偼姶岝惈傕桳偟偰偍傝丄僷僢僔儀乕僔儑儞偩偗偱側偔丄RGB僒僽僺僋僙儖傪巇愗傞僶儞僋偲偟偰傕婡擻偡傞丅側偍丄偙偺億儕儅乕偼堦斒揑側桳婡梟攠偵偼梟夝偟側偄偨傔丄忋晹偵椨岝億儕儅乕僀儞僋傪揾晍丒報嶞偟偰傕梟夝偟側偄丅偙偺屻丄屻岺掱偱偁傞崅暘巕敪岝憌宍惉岺掱偺報嶞惛搙傪曗姰偡傞偨傔丄O2僈僗偱ITO夋慺揹嬌傪恊悈惈偵丄CF4僈僗偱僶儞僋懁暻傪潧悈惈偵昞柺夵幙偡傞丅懕偄偰丄RGB偺椨岝億儕儅乕傪ITO夋慺揹嬌忋偵僀儞僋僕僃僢僩僾儕儞僥傿儞僌朄偵傛傝枌岤50nm偱僟僀儗僋僩報嶞偡傞丅恾3偼巊梡偟偨椢怓椨岝億儕儅乕偺暘巕峔憿偱丄椨岝婎偩偗偱側偔丄揹巕桝憲婎丄儂乕儖桝憲婎傕嫟廳崌偝傟偰偄傞丅偙偺屻丄LiF(1nm)/Al(150nm)傪忲拝偟偰僇僜乕僪傪惉枌偡傞丅偪側傒偵丄奜晹検巕岠棪偼愒怓偑13亾丄椢怓偑14亾丄惵怓偑12亾偩偭偨丅嵟屻偵僶儕傾僼傿儖儉傪儔儈僱乕僩偟偰屌懱晻巭偟偨屻丄僉儍儕傾僈儔僗偐傜僷僱儖傪儕儕乕僗偡傞巇慻傒丅僾儘僙僗壏搙偼儅僢僋僗130亷偵梷惂偟丄PEN僼傿儖儉偺擬曄宍傪儈僯儅儉壔偟偨丅

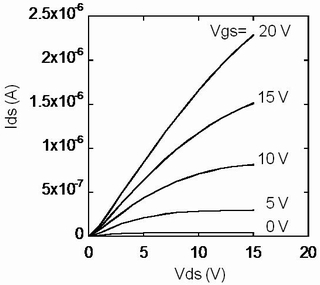

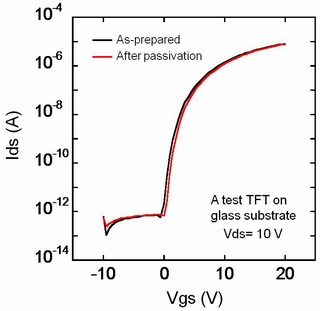

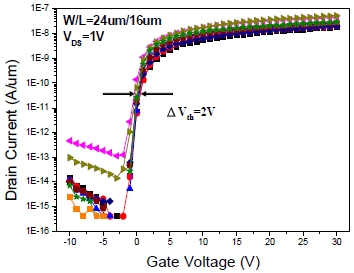

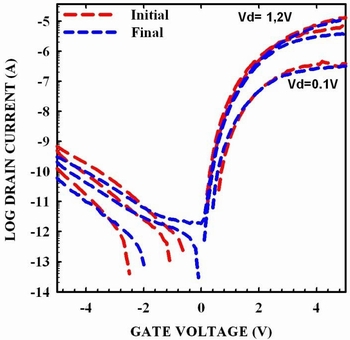

丂恾4偼a-IGZO-TFT偺僩儔儞僗僼傽乕摿惈偱丄OFF揹棳偼10-12A埲壓偲偒傢傔偰彫偝偐偭偨丅懠曽丄ON揹棳偼10-6A埲忋偱丄ON/OFF揹棳儗僔僆偼106偲崅偄抣偑摼傜傟偨丅 丂偲偙傠偱丄桳婡EL偺婸搙偼僪儔僀僽價儞僌TFT偐傜偺僪儗僀儞揹棳偵傛偭偰惂屼偡傞丅偙偺抣偑僨傿僗僾儗僀偺僐儞僩儔僗僩摿惈偵捈寢偡傞丅帋嶌僨僶僀僗偱偼丄恾5偺傛偆偵僪儗僀儞揹埑15V偱僪儗僀儞揹棳偑朞榓偡傞椙岲側弌椡摿惈偑摼傜傟偨丅偙偺朞榓椞堟偐傜尒愊傕傜傟偨僉儍儕傾儌價儕僥傿偼3cm2/V掱搙偩偭偨丅偙傟傜偺寢壥偼掅壏僾儘僙僗偱宍惉偟偨億儕儅乕僎乕僩愨墢枌偱傕桳婡ELD傪廫暘僪儔僀僽偱偒傞偙偲傪堄枴偟偰偄傞丅

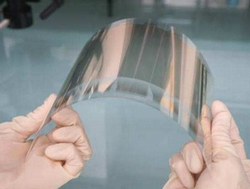

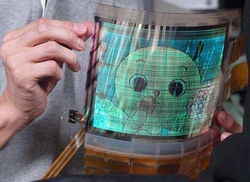

丂尋媶僌儖乕僾偼丄a-IGZO-TFT忋偵桳婡僷僢僔儀乕僔儑儞傪僟僀儗僋僩宍惉偟偨嵺偺塭嬁傕挷傋偨丅恾6偼僷僢僔儀乕僔儑儞宍惉慜偲宍惉屻偺僈儔僗惢a-IGZO-TFT偺摿惈偱丄僷僢僔儀乕僔儑儞宍惉屻偵僞乕儞僆儞揹埑偑傢偢偐偵僔僼僩偟偰偄傞傕偺偺丄僞乕儞僆僼揹棳偼傑偭偨偔曄壔偟偰偄側偄偙偲偑傢偐傞丅忋婰偺寢壥偼姶岝惈億儕儅乕傪梡偄偰僷僢僔儀乕僔儑儞傪宍惉偟偰傕a-IGZO-TFT偺摿惈偑傎偲傫偳曄壔偟側偄偙偲傪帵嵈偡傞丅 丂崱夞帋嶌偟偨偺偼8宆VGA僷僱儖偱丄僩乕僞儖岤傪0.3噊偵敄宆壔丅PEN僼傿儖儉丄偦偟偰億儕儅乕僎乕僩愨墢枌偲億儕儅乕僷僢僔儀乕僔儑儞仌僶儞僋傪梡偄傞偙偲偵傛傝丄幨恀2偺傛偆偵僼儗僉僔僽儖壔偡傞偙偲偵惉岟偟偨丅 悽奅偱弶傔偰Roll to Roll曽幃偱a-IGZO-TFT傪帋嶌 丂Industrial Technology Research Institute(ITRI)偼僼儗僉僔僽儖僨傿僗僾儗僀岦偗偲偟偰悽奅偱弶傔偰Roll to Roll曽幃偱a-IGZO-TFT傪嶌惢丄僙僌儊儞僩嬱摦偺4.3宆揹婥塲摦僨傿僗僾儗僀傪僪儔僀僽偡傞偙偲偵惉岟偟偨丅

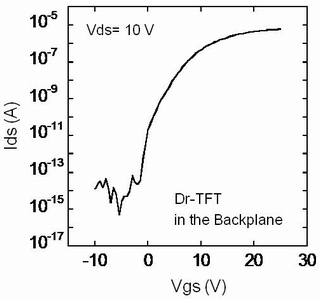

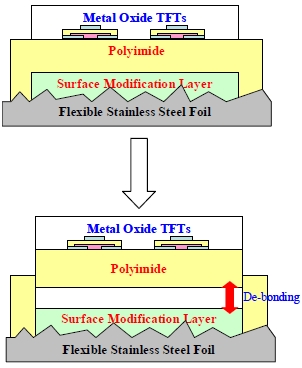

丂僒僽僗僩儗乕僩偵偼3憌峔憿偺僼儗僉僔僽儖僴僀僽儕僢僪婎斅傪巊梡偟偨丅嬶懱揑偵偼僉儍儕傾婎斅偵僗僥儞儗僗敁傪巊梡偟丄偦偺忋晹偵僾儔僫儕僛乕僔儑儞仌攳棧憌偲偟偰婡擻偡傞昞柺夵幙憌傪揾晍丅嵟屻偵丄PI枌傪揾晍偟峝壔偝偣偰僼儗僉僔僽儖僒僽僗僩儗乕僩偵偟偨丅偙偺僴僀僽儕僢僪僼儗僉僔僽儖婎斅忋偵Roll to Roll曽幃偱a-IGZO-TFT傪嶌惢丅嵟屻偵丄撈帺偺攳棧朄偵傛偭偰僗僥儞儗僗敁偐傜PI儀乕僗偺a-IGZO-TFT傪儕儕乕僗偟偨丅 丂偲偙傠偱丄僎乕僩儕乕僋揹棳偼Roll to Roll曽幃TFT偱偼僋儕僥傿僇儖側栤戣偲側傞丅椺偊偽僎乕僩傊偺報壛揹奅偑1MV/cm埲壓偺応崌丄堦斒揑偵嫋梕偝傟傞儕乕僋揹棳偼10.8A/cm2掱搙偱偁傞丅偟偐偟丄僎乕僩愨墢憌偲偟偰幒壏偱僗僷僢僞惉枌偟偨SiO2枌(枌岤200nm)偼壛擬惉枌偟偨応崌偵斾傋枌枾搙偑晄廫暘偱丄儕乕僋揹棳傕10.6A/cm2(@1MV/cm)偲崅偄抣傪帵偡丅懠曽丄SiO2/Al2O3(30nm)僟僽儖僎乕僩愨墢枌傪梡偄偨応崌丄儕乕僋揹棳偼10.7A/cm2(@1MV/cm)偩偭偨丅偮傑傝丄偳偪傜傕攋夡揹奅偼1.5MV/cm掱搙偲廫暘偱偼側偄丅偦偙偱丄僎乕僩愨墢枌偼Roll to Roll懳墳僗僷僢僞憰抲偱偼側偔婎斅壏搙200亷偱僾儔僘儅CVD惉枌偟偨丅

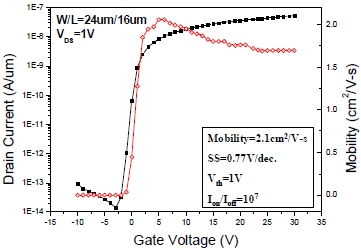

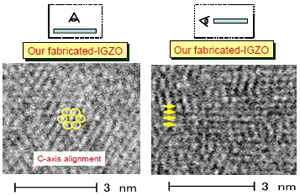

丂幨恀3偼僇儔乕儗僗偺PI枌傪揾晍偟偨條巕偱丄PI枌偺抂晹偼昞柺夵幙憌偺壓晹偵傑偱怹摟偟丄僗僥儞儗僗敁偲捈愙愙偟偰偄傞丅尦棃丄PI偲僗僥儞儗僗敁偼枾拝惈偑崅偔丄TFT僾儘僙僗拞偵攳棧偡傞偙偲偼側偄丅偦偺偨傔丄奺儗僀儎乕娫偺廳偹崌傢偣惛搙傪5兪m埲撪偵梷惂偱偒偨丅偙傟偼丄擬朿挘偵婲場偡傞梫場傪揙掙揑偵攔彍偟偨偨傔偱偁傞丅傑偨丄PI僼傿儖儉偲昞柺夵幙憌偼愙拝惈偑掅偄偨傔丄偦偺奅柺偐傜梕堈偵PI儀乕僗a-IGZO-TFT僨僶僀僗傪儕儕乕僗偡傞偙偲偑偱偒傞丅 丂恾8偼嶌惢偟偨a-IGZO-TFT(僠儍僱儖挿16兪m丄僠儍僱儖暆24兪m)偺僩儔儞僗僼傽乕摿惈偱丄儌價儕僥傿偼2.1cm2/V丄SS僼傽僋僞乕偼0.77V/decade丄Vth偼1V丄ON/OFF揹棳儗僔僆偼107偩偭偨丅傑偨丄恾9偺傛偆偵150亊150噊僒僀僘偵偍偗傞Vth偺曃嵎偼栺2V偩偭偨丅 寢徎惈IGZO-TFT偺幚椡偼丠 丂巁壔暔TFT偱嵟戝偺娭怱傪廤傔偨偺偑僔儍乕僾偲敿摫懱僄僱儖僊乕尋媶強偑敪昞偟偨寢徎惈IGZO-TFT丅SID 2012奐嵜捈慜偵僾儗僗敪昞偟偨偙偲傕偁傝丄崅偄拲栚傪廤傔偨偑丄寢榑偐傜偄偆偲尋媶惉壥偺傒傪敪昞偟偨偵夁偓偢丄挳島幰傪娷傔戞嶰幰揑偵偼徚壔晄椙偺姶偑斲傔側偐偭偨丅 丂怴偨偵敪尒偟偨偺偼C幉攝岦偟偨IGZO巁壔暔敿摫懱偱丄CAAC(C-Axis Aligned Crystal)偲柤偯偗偨丅僐儞儀儞僔儑僫儖側傾儌儖僼傽僗偱偼側偔扨寢徎偵嬤偔丄a-b僾儗乕儞偼儌僓僀僋僷僞乕儞偱偁傝丄僌儗僀儞僶僂儞僟儕乕偑娤嶡偝傟側偄丅偙傟偵懳偟丄懡寢徎偼堦斒揑偵儔儞僟儉攝岦偟偰偍傝丄僌儗僀儞僶僂儞僟儕乕偑娤嶡偝傟傞丅

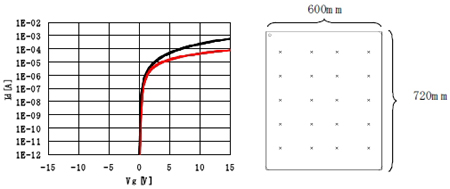

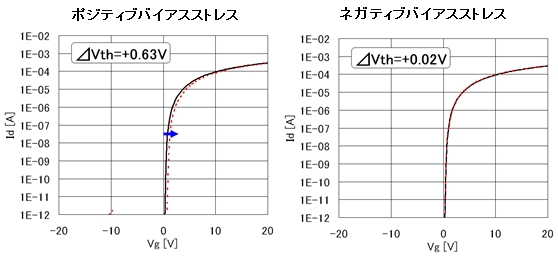

丂幨恀4偼CAAC IGZO枌 (In:Ga:Zn-1:1:1)偺TEM憸偱丄C幉曽岦偐傜傒傞偲偦偺寢徎偼榋妏峔憿偵傒偊傞丅傑偨丄XRD夝愅偱偼(009)偵僺乕僋僗儁僋僩儖傪帵偟偨丅偝傜偵丄枌枾搙傪挷傋偨偲偙傠6.22g/cm3偲扨寢徎(6.375 g/cm3)偵嬤偐偭偨丅偮傑傝丄扨寢徎儔僀僋偲偄偊傞丅 丂偙偺偨傔丄CAAC傪梡偄傟偽TFT偺怣棅惈偑岦忋偱偒傞偲峫偊偨丅偦偙偱丄IGZO-TFT傪嶌惢偟摿惈傪昡壙偟偨丅恾10偼600亊720噊僈儔僗婎斅偺摿惈曃嵎丄恾11偼僶僀傾僗僗僩儗僗僥僗僩偺昡壙寢壥偱丄僎乕僩僶僀傾僗僗僩儗僗僥僗僩偱傕Vth曄摦偑偒傢傔偰彮側偔丄怣棅惈偑崅偄偙偲偑傢偐傞丅

丂忋婰偺惉壥傪庴偗丄CAAC IGZO-TFT嬱摦偺13.5宆僋儚僢僪僼儖HD(3840亊2160夋慺)桳婡ELD傪帋嶌偟偨丅桳婡EL偼敀怓EL亄僇儔乕僼傿儖僞乕曽幃傪嵦梡丅TFT偼5T-1C峔惉偱丄僗僉儍儞僪儔僀僶夞楬傪僈儔僗婎斅忋偵價儖僩僀儞偟偨丅 丂偝傜偵丄僉儍儕傾僈儔僗忋偵CAAC IGZO-TFT傪嶌惢偟偨屻丄僼儗僉僔僽儖僒僽僗僩儗乕僩偵揮幨偟僗僥儞儗僗敁偱晻巭偟偨僼儗僉僔僽儖桳婡ELD傕帋嶌丅嶲峫偲偟偰丄幨恀5偵帋嶌偟偨13.5宆僼儗僉僔僽儖僷僱儖(960亊540夋慺)傪帵偡丅 丂埲忋偑敪昞偺奣梫偱丄CAAC IGZO枌傪偳偺傛偆偵嶌惢偡傞偺偐偵偮偄偰堦愗尵媦偑側偄偺偑巆擮偵姶偠偨丅 揾晍宆巁壔暔TFT偺僾儘僙僗壏搙傪230亷偵梷惂

丂僾儕儞僞僽儖巁壔暔TFT偱偼丄娯崙偺Kyung Hee University偑寽埬偲側偭偰偄傞從惉壏搙傪230亷偵掅壓偝偣偨偙偲傪曬崘偟偨丅 丂尋媶僌儖乕僾偼埲慜丄ZTO(Zinc Tin Oxide)枌傪350亷偱從惉偟偰巁壔暔敿摫懱偵偡傞偙偲偵惉岟丅崱夞丄偝傜側傞掅壏從惉壔傪恾傞偨傔丄揧壛梟攠傪嵟揔壔偡傞偲偲傕偵丄ZTO偵In傪壛偊偨IZTO(Indium Zinc Tin Oxide)傪梡偄傞偙偲偵偟偨丅 丂帋嶌僨僶僀僗偼丄傑偢僈儔僗婎斅忋偵Mo枌傪枌岤40nm偱僗僷僢僞儕儞僌惉枌偟僼僅僩儕僜偱僷僞乕僯儞僌偟偰僎乕僩揹嬌傪宍惉丅懕偄偰丄AlOx梟塼傪僗僺儞僐乕僩偟230亷偱從惉丅偙傟傪寁5夞孞傝曉偟偰枌岤傪77nm偵傑偱懲愊偟偰僎乕僩愨墢枌傪宍惉偟偨丅師偵僐儞僞僋僩儂乕儖傪宍惉偟偨屻丄IZO枌傪僗僷僢僞惉枌偟僼僅僩儕僜偱僷僞乕僯儞僌偟偰僜乕僗/僪儗僀儞傪宍惉丅嵟屻偵丄InCl3丄SnCl2丄ZnCl2傪梟攠偲嬌彮検偺巁偵梟夝偝偣偨墫壔暔僾儕僇乕僒梟塼傪僗僺儞僐乕僩偟200亷亊2帪娫從惉偟偰巁壔暔敿摫懱憌傪宍惉偟偨丅僠儍僱儖挿偼6兪m丄僠儍僱儖暆偼100兪m偱偁傞丅

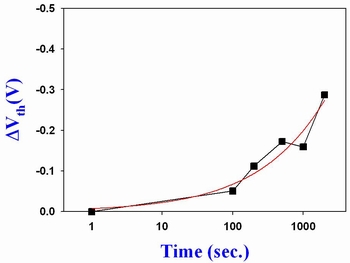

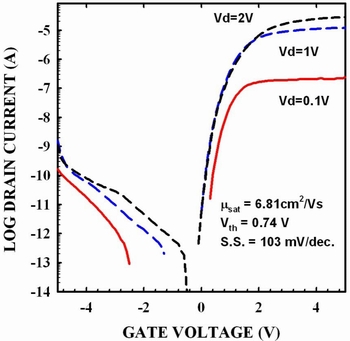

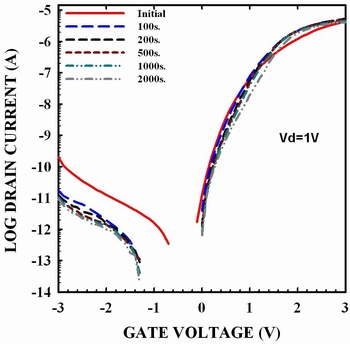

丂恾12偼偦偺僩儔儞僗僼傽乕摿惈偱丄朞榓椞堟偐傜尒愊傕傜傟偨僉儍儕傾儌價儕僥傿偼6.81cm2/V偩偭偨丅傑偨丄Vth偼0.74V丄SS僼傽僋僞乕偼103mV/dec丄ON/OFF揹棳儗僔僆偼107偑摼傜傟偨丅恾13偼僱僈僥傿僽僶僀傾僗僗僩儗僗僥僗僩偺寢壥偱丄僱僈僥傿僽僶僀傾僗傪2000昩報壛屻偺Vth僔僼僩偼0.3V偵夁偓側偐偭偨丅 丂恾14偼僶僀傾僗僗僩儗僗傪報壛偣偢偵婸搙9000cd/m2偺僶僢僋儔僀僩偐傜敀怓岝傪徠幩偟偨嵺偺摿惈偱丄岝徠幩偵傛傞摿惈曄摦偼偒傢傔偰彮側偔丄傢偢偐偵Vth偑僱僈僥傿僽曽岦偵僔僼僩偟偨偵夁偓側偐偭偨丅偝傜偵丄VGS亖亅3V傪報壛偟側偑傜敀怓岝傪徠幩偟偨嵺偺摿惈曄摦傕恾15偺傛偆偵柍帇偱偒傞儗儀儖偩偭偨丅 嶲峫暥專 |

||||||||||||||||||||||||||||

仸應挿婡擻 仸奜娤専嵏婡擻 |